4H-N HPSI SiC Wafer 6H-N 6H-P 3C-N SiC Epitakzialwafer fir MOS oder SBD

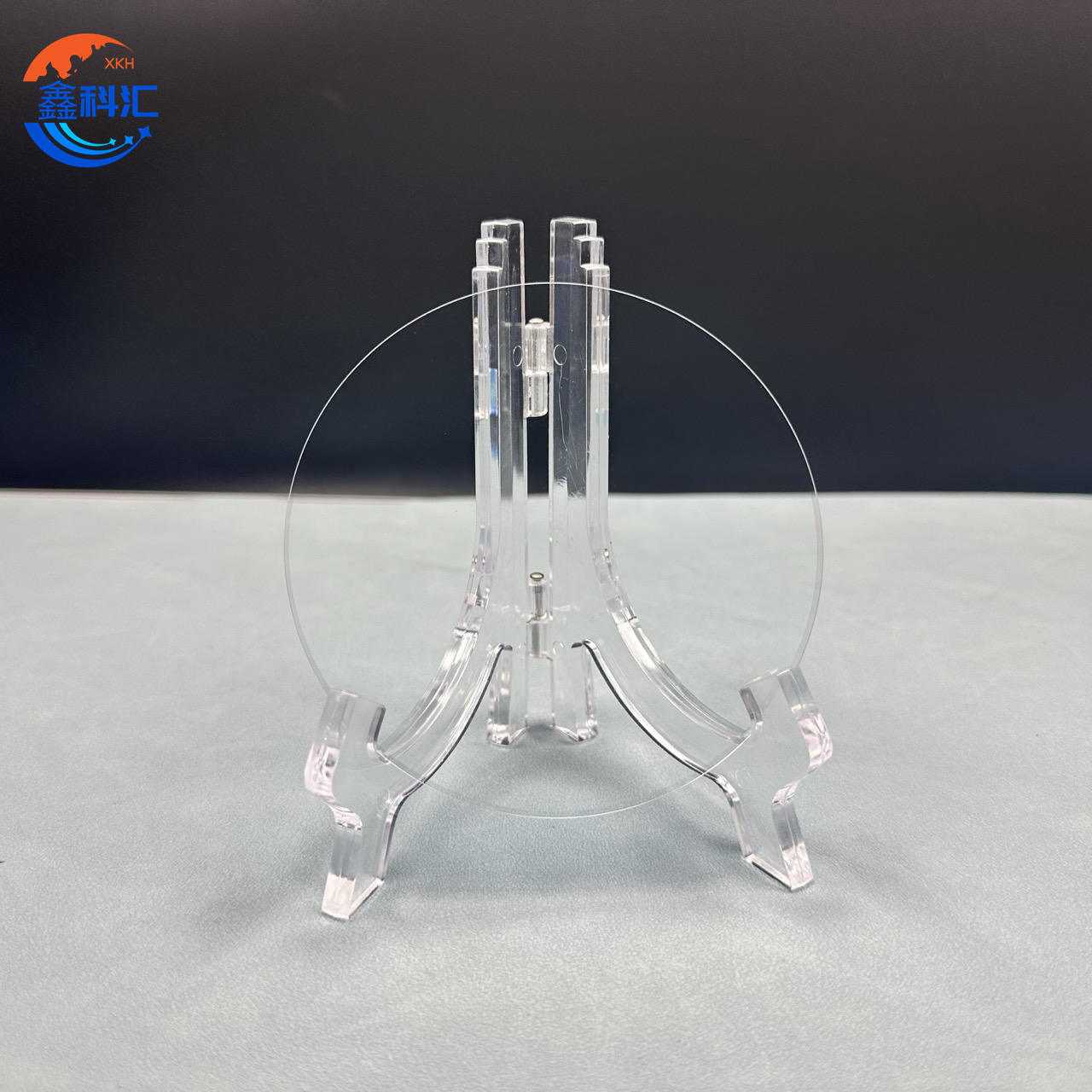

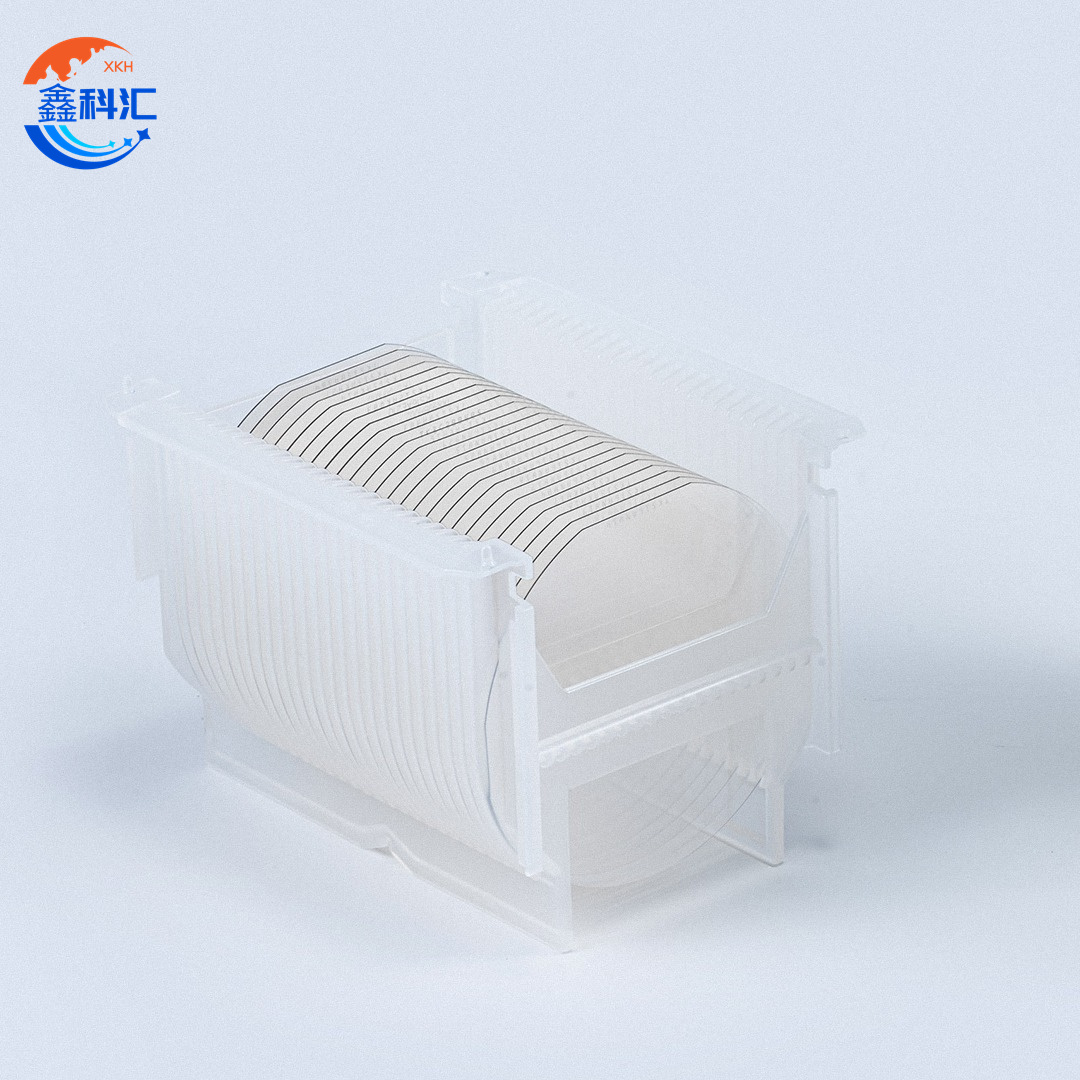

SiC Substrat SiC Epi-Wafer Kuerz

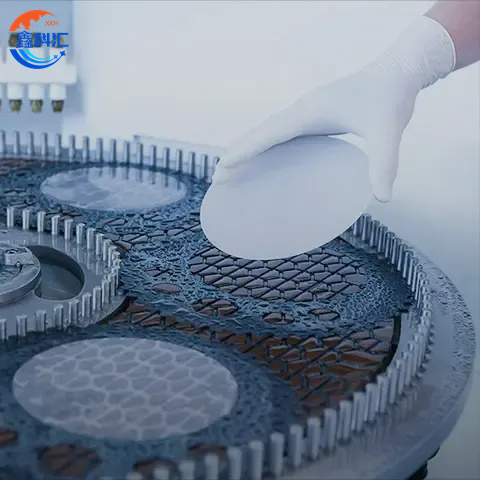

Mir bidden e komplette Portfolio vun héichwäertege SiC-Substrater a SIC-Waferen a verschiddene Polytypen an Dotierprofiler - dorënner 4H-N (n-Typ leetend), 4H-P (p-Typ leetend), 4H-HPSI (héichreine Hallefisolatioun) a 6H-P (p-Typ leetend) - an Duerchmiesser vu 4″, 6″ an 8″ bis zu 12″. Nieft blanne Substrater liwweren eis wäertvoll Epi-Wafer-Wuesstumsservicer epitaktesch (epi) Waferen mat streng kontrolléierter Déckt (1–20 µm), Dotierkonzentratiounen an Defektdichten.

All Sic-Wafer an Epi-Wafer ënnerleien enger rigoréiser In-Line-Inspektioun (Mikropäifdicht <0,1 cm⁻², Uewerflächenrauheet Ra <0,2 nm) a kompletter elektrescher Charakteriséierung (CV, Widderstandsmapping), fir eng aussergewéinlech Kristalluniformitéit a Leeschtung ze garantéieren. Egal ob se fir Leeschtungselektronikmoduler, Héichfrequenz-HF-Verstärker oder optoelektronesch Geräter (LEDs, Photodetekteren) benotzt ginn, eis SiC-Substrat- an Epi-Wafer-Produktlinne liwweren déi Zouverlässegkeet, thermesch Stabilitéit an Duerchbrochfestigkeit, déi vun den haitegsten Uwendungen erfuerderlech sinn.

Eegeschaften an Uwendungen vum SiC-Substrat vum Typ 4H-N

-

4H-N SiC-Substrat Polytyp (Hexagonal) Struktur

Eng breet Bandlück vun ~3,26 eV garantéiert eng stabil elektresch Leeschtung a thermesch Robustheet ënner héijen Temperaturen a Konditioune mat héijem elektresche Feld.

-

SiC-SubstratN-Typ Doping

Genee kontrolléiert Stickstoffdotierung ergëtt Trägerkonzentratioune vun 1×10¹⁶ bis 1×10¹⁹ cm⁻³ an Elektronemobilitéite bei Raumtemperatur vu bis zu ~900 cm²/V·s, wouduerch d'Leetungsverloschter miniméiert ginn.

-

SiC-SubstratBreet Widderstand & Uniformitéit

Verfügbare Widderstandsberäich vun 0,01–10 Ω·cm a Waferdicken vun 350–650 µm mat enger Toleranz vun ±5% souwuel bei der Dotierung wéi och bei der Déckt – ideal fir d'Fabrikatioun vun Héichleistungs-Apparater.

-

SiC-SubstratUltra-niddreg Defektdicht

Mikropäifdicht < 0,1 cm⁻² an Basal-Plane-Dislokatiounsdicht < 500 cm⁻², wat eng Geräterausbezuelung vun > 99% an eng iwwerleeën Kristallintegritéit liwwert.

- SiC-SubstratAussergewéinlech thermesch Konduktivitéit

Eng Wärmeleitfäegkeet vu bis zu ~370 W/m·K erliichtert eng effizient Hëtztentfernung, erhéicht d'Zouverlässegkeet an d'Leeschtungsdicht vum Apparat.

-

SiC-SubstratZil-Applikatiounen

SiC MOSFETs, Schottky-Dioden, Leeschtungsmoduler an HF-Apparater fir Undriff vun Elektroautoen, Solarwechselrichter, Industrieundriff, Traktiounssystemer an aner usprochsvoll Mäert am Beräich vun der Leeschtungselektronik.

Spezifikatioun vun 6 Zoll 4H-N Typ SiC Wafer | ||

| Immobilie | Null MPD Produktiounsgrad (Z-Grad) | Dummy-Klass (Klass D) |

| Grad | Null MPD Produktiounsgrad (Z-Grad) | Dummy-Klass (Klass D) |

| Duerchmiesser | 149,5 mm - 150,0 mm | 149,5 mm - 150,0 mm |

| Poly-Typ | 4H | 4H |

| Déckt | 350 µm ± 15 µm | 350 µm ± 25 µm |

| Wafer Orientéierung | Off-axis: 4,0° Richtung <1120> ± 0,5° | Off-axis: 4,0° Richtung <1120> ± 0,5° |

| Mikropäifdicht | ≤ 0,2 cm² | ≤ 15 cm² |

| Widderstandsfäegkeet | 0,015 - 0,024 Ω·cm | 0,015 - 0,028 Ω·cm |

| Primär flaach Orientéierung | [10-10] ± 50° | [10-10] ± 50° |

| Primär flaach Längt | 475 mm ± 2,0 mm | 475 mm ± 2,0 mm |

| Randausgrenzung | 3 mm | 3 mm |

| LTV/TIV / Béi / Ketten | ≤ 2,5 µm / ≤ 6 µm / ≤ 25 µm / ≤ 35 µm | ≤ 5 µm / ≤ 15 µm / ≤ 40 µm / ≤ 60 µm |

| Rauheet | Polnesch Ra ≤ 1 nm | Polnesch Ra ≤ 1 nm |

| CMP Ra | ≤ 0,2 nm | ≤ 0,5 nm |

| Kantrëss duerch héichintensivt Liicht | Kumulativ Längt ≤ 20 mm, eenzel Längt ≤ 2 mm | Kumulativ Längt ≤ 20 mm, eenzel Längt ≤ 2 mm |

| Sechseckplacken duerch héichintensivt Liicht | Kumulativ Fläch ≤ 0,05% | Kumulativ Fläch ≤ 0,1% |

| Polytypberäicher duerch héichintensivt Liicht | Kumulativ Fläch ≤ 0,05% | Kumulativ Fläch ≤ 3% |

| Visuell Kuelestoffinklusiounen | Kumulativ Fläch ≤ 0,05% | Kumulativ Fläch ≤ 5% |

| Siliziumoberfläche kraazt duerch héichintensivt Liicht | Kumulativ Längt ≤ 1 Waferduerchmiesser | |

| Kantchips duerch héichintensivt Liicht | Keen erlaabt ≥ 0,2 mm Breet an Déift | 7 erlaabt, ≤ 1 mm all |

| Verrécklung vun der Gewënnschraube | < 500 cm³ | < 500 cm³ |

| Kontaminatioun vun der Siliziumoberfläche duerch héichintensivt Liicht | ||

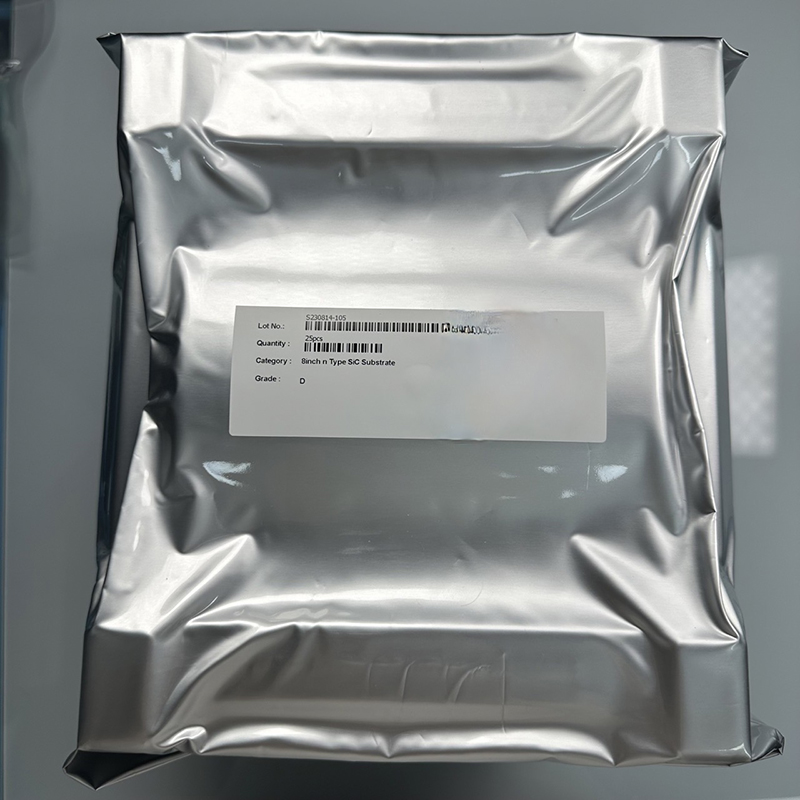

| Verpackung | Multi-Wafer Kassett oder Eenzelwafer Behälter | Multi-Wafer Kassett oder Eenzelwafer Behälter |

Spezifikatioun vun 8 Zoll 4H-N Typ SiC Wafer | ||

| Immobilie | Null MPD Produktiounsgrad (Z-Grad) | Dummy-Klass (Klass D) |

| Grad | Null MPD Produktiounsgrad (Z-Grad) | Dummy-Klass (Klass D) |

| Duerchmiesser | 199,5 mm - 200,0 mm | 199,5 mm - 200,0 mm |

| Poly-Typ | 4H | 4H |

| Déckt | 500 µm ± 25 µm | 500 µm ± 25 µm |

| Wafer Orientéierung | 4,0° Richtung <110> ± 0,5° | 4,0° Richtung <110> ± 0,5° |

| Mikropäifdicht | ≤ 0,2 cm² | ≤ 5 cm² |

| Widderstandsfäegkeet | 0,015 - 0,025 Ω·cm | 0,015 - 0,028 Ω·cm |

| Edel Orientéierung | ||

| Randausgrenzung | 3 mm | 3 mm |

| LTV/TIV / Béi / Ketten | ≤ 5 µm / ≤ 15 µm / ≤ 35 µm / 70 µm | ≤ 5 µm / ≤ 15 µm / ≤ 35 µm / 100 µm |

| Rauheet | Polnesch Ra ≤ 1 nm | Polnesch Ra ≤ 1 nm |

| CMP Ra | ≤ 0,2 nm | ≤ 0,5 nm |

| Kantrëss duerch héichintensivt Liicht | Kumulativ Längt ≤ 20 mm, eenzel Längt ≤ 2 mm | Kumulativ Längt ≤ 20 mm, eenzel Längt ≤ 2 mm |

| Sechseckplacken duerch héichintensivt Liicht | Kumulativ Fläch ≤ 0,05% | Kumulativ Fläch ≤ 0,1% |

| Polytypberäicher duerch héichintensivt Liicht | Kumulativ Fläch ≤ 0,05% | Kumulativ Fläch ≤ 3% |

| Visuell Kuelestoffinklusiounen | Kumulativ Fläch ≤ 0,05% | Kumulativ Fläch ≤ 5% |

| Siliziumoberfläche kraazt duerch héichintensivt Liicht | Kumulativ Längt ≤ 1 Waferduerchmiesser | |

| Kantchips duerch héichintensivt Liicht | Keen erlaabt ≥ 0,2 mm Breet an Déift | 7 erlaabt, ≤ 1 mm all |

| Verrécklung vun der Gewënnschraube | < 500 cm³ | < 500 cm³ |

| Kontaminatioun vun der Siliziumoberfläche duerch héichintensivt Liicht | ||

| Verpackung | Multi-Wafer Kassett oder Eenzelwafer Behälter | Multi-Wafer Kassett oder Eenzelwafer Behälter |

4H-SiC ass en héichperformant Material, dat fir Leeschtungselektronik, HF-Geräter an Héichtemperaturapplikatioune benotzt gëtt. Den "4H" bezitt sech op d'Kristallstruktur, déi hexagonal ass, an den "N" weist en Dotierungstyp un, deen benotzt gëtt fir d'Leeschtung vum Material ze optimiséieren.

Den4H-SiCTyp gëtt dacks benotzt fir:

Leeschtungselektronik:Benotzt a Geräter wéi Dioden, MOSFETs an IGBTs fir Undriffssystemer fir Elektroautoen, Industriemaschinnen a Systemer fir erneierbar Energien.

5G Technologie:Mat der Nofro vum 5G fir Héichfrequenz- a Héicheffizienzkomponenten, mécht d'Fäegkeet vu SiC, héich Spannungen ze handhaben a bei héijen Temperaturen ze funktionéieren, et ideal fir Basisstatiouns-Leeschtungsverstärker an HF-Geräter.

Solarenergiesystemer:Déi exzellent Energieveraarbechtungseigenschaften vu SiC si ideal fir photovoltaesch (Solarenergie-) Wechselrichter a Konverter.

Elektroautoen (EVs):SiC gëtt wäit verbreet an EV-Undriffssystemer fir eng méi effizient Energiekonversioun, eng méi niddreg Hëtzeproduktioun a méi héich Leeschtungsdicht benotzt.

Eegeschaften an Uwendung vum SiC-Substrat 4H Hallefisolatiounstyp

Eegeschaften:

-

Techniken fir d'Kontroll vun der Dicht ouni MikropäifenGarantéiert d'Feele vu Mikropäifen, verbessert d'Substratqualitéit.

-

Monokristallin KontrolltechnikenGarantéiert eng Eenzelkristallstruktur fir verbessert Materialeegeschafte.

-

Technike fir d'Kontroll vun InklusiounenMiniméiert d'Präsenz vun Ongereinheeten oder Inklusiounen a garantéiert e reint Substrat.

-

Techniken fir d'Kontroll vum WidderstandErlaabt eng präzis Kontroll vum elektresche Widderstand, wat entscheedend fir d'Leeschtung vum Apparat ass.

-

Techniken fir d'Reguléierung an d'Kontroll vun OnreinheetenReguléiert a limitéiert d'Aféierung vun Ongereinheeten, fir d'Integritéit vum Substrat ze erhalen.

-

Technike fir d'Kontroll vun der Stufbreet vum SubstratBitt eng präzis Kontroll iwwer d'Schrëttbreet a garantéiert Konsistenz um ganze Substrat

Spezifikatioun vum 6 Zoll 4H-Semi-SiC-Substrat | ||

| Immobilie | Null MPD Produktiounsgrad (Z-Grad) | Dummy-Klass (Klass D) |

| Duerchmiesser (mm) | 145 mm - 150 mm | 145 mm - 150 mm |

| Poly-Typ | 4H | 4H |

| Déckt (um) | 500 ± 15 | 500 ± 25 |

| Wafer Orientéierung | Op der Achs: ±0,0001° | Op der Achs: ±0,05° |

| Mikropäifdicht | ≤ 15 cm-2 | ≤ 15 cm-2 |

| Widderstand (Ωcm) | ≥ 10E3 | ≥ 10E3 |

| Primär flaach Orientéierung | (0-10)° ± 5,0° | (10-10)° ± 5,0° |

| Primär flaach Längt | Kerb | Kerb |

| Kantenausgrenzung (mm) | ≤ 2,5 µm / ≤ 15 µm | ≤ 5,5 µm / ≤ 35 µm |

| LTV / Schossel / Warp | ≤ 3 µm | ≤ 3 µm |

| Rauheet | Poléiert Ra ≤ 1,5 µm | Poléiert Ra ≤ 1,5 µm |

| Kantchips duerch héichintensivt Liicht | ≤ 20 µm | ≤ 60 µm |

| Hëtztplacken duerch héichintensivt Liicht | Kumulativ ≤ 0,05% | Kumulativ ≤ 3% |

| Polytypberäicher duerch héichintensivt Liicht | Visuell Kuelestoffinklusiounen ≤ 0,05% | Kumulativ ≤ 3% |

| Siliziumoberfläche kraazt duerch héichintensivt Liicht | ≤ 0,05% | Kumulativ ≤ 4% |

| Kantchips duerch héichintensivt Liicht (Gréisst) | Net erlaabt > 02 mm Breet an Déift | Net erlaabt > 02 mm Breet an Déift |

| D'Hëllefsschraufdilatatioun | ≤ 500 µm | ≤ 500 µm |

| Kontaminatioun vun der Siliziumoberfläche duerch héichintensivt Liicht | ≤ 1 x 10^5 | ≤ 1 x 10^5 |

| Verpackung | Multi-Wafer-Kassett oder Eenzelwafer-Behälter | Multi-Wafer-Kassett oder Eenzelwafer-Behälter |

Spezifikatioun vum 4-Zoll 4H-Halbisoléierende SiC-Substrat

| Parameter | Null MPD Produktiounsgrad (Z-Grad) | Dummy-Klass (Klass D) |

|---|---|---|

| Physikalesch Eegeschaften | ||

| Duerchmiesser | 99,5 mm – 100,0 mm | 99,5 mm – 100,0 mm |

| Poly-Typ | 4H | 4H |

| Déckt | 500 μm ± 15 μm | 500 μm ± 25 μm |

| Wafer Orientéierung | Op der Achs: <600h > 0,5° | Op der Achs: <000h > 0,5° |

| Elektresch Eegeschaften | ||

| Mikropäifdicht (MPD) | ≤1 cm⁻² | ≤15 cm⁻² |

| Widderstandsfäegkeet | ≥150 Ω·cm | ≥1,5 Ω·cm |

| Geometresch Toleranzen | ||

| Primär flaach Orientéierung | (0x10) ± 5,0° | (0x10) ± 5,0° |

| Primär flaach Längt | 52,5 mm ± 2,0 mm | 52,5 mm ± 2,0 mm |

| Sekundär flaach Längt | 18,0 mm ± 2,0 mm | 18,0 mm ± 2,0 mm |

| Sekundär flaach Orientéierung | 90° mat der rietser Säit vun der Prime-Flaach ± 5,0° (Si-Front no uewen) | 90° mat der rietser Säit vun der Prime-Flaach ± 5,0° (Si-Front no uewen) |

| Randausgrenzung | 3 mm | 3 mm |

| LTV / TTV / Béi / Ketten | ≤2,5 μm / ≤5 μm / ≤15 μm / ≤30 μm | ≤10 μm / ≤15 μm / ≤25 μm / ≤40 μm |

| Uewerflächenqualitéit | ||

| Uewerflächenrauheet (Polnesch Ra) | ≤1 nm | ≤1 nm |

| Uewerflächenrauheet (CMP Ra) | ≤0,2 nm | ≤0,2 nm |

| Rëss um Rand (Héichintensivt Liicht) | Net erlaabt | Kumulativ Längt ≥10 mm, eenzel Rëss ≤2 mm |

| Defekter vun der sechseckeger Placke | ≤0,05% kumulativ Fläch | ≤0,1% kumulativ Fläch |

| Polytyp-Inklusiounsgebidder | Net erlaabt | ≤1% kumulativ Fläch |

| Visuell Kuelestoffinklusiounen | ≤0,05% kumulativ Fläch | ≤1% kumulativ Fläch |

| Kratzer op der Silikonoberfläche | Net erlaabt | Kumulativ Längt vun ≤1 Waferduerchmiesser |

| Kantchips | Net erlaabt (≥0,2 mm Breet/Déift) | ≤5 Chips (jeeweils ≤1 mm) |

| Kontaminatioun vun der Siliziumoberfläche | Net spezifizéiert | Net spezifizéiert |

| Verpackung | ||

| Verpackung | Multi-Wafer-Kassett oder Eenzel-Wafer-Behälter | Multi-Wafer-Kassett oder |

Applikatioun:

DenSiC 4H Hallefisolatiounssubstratergi virun allem an elektroneschen Apparater mat héijer Leeschtung an héijer Frequenz benotzt, besonnesch an derHF-FeldDës Substrate si fir verschidden Uwendungen entscheedend, dorënnerMikrowellenkommunikatiounssystemer, Phased-Array-Radar, andrahtlos elektresch DetektorenHir héich thermesch Leetfäegkeet an exzellent elektresch Eegeschafte maachen se ideal fir usprochsvoll Uwendungen an der Leeschtungselektronik a Kommunikatiounssystemer.

Eegeschaften an Uwendungen vun SiC Epi-Wafer vum Typ 4H-N

Eegeschaften an Uwendungen vum SiC 4H-N Typ Epi Wafer

Eegeschafte vun der SiC 4H-N Typ Epi Wafer:

Materialzesummesetzung:

SiC (Siliziumkarbid)Bekannt fir seng aussergewéinlech Häert, héich thermesch Leetfäegkeet an exzellent elektresch Eegeschaften, ass SiC ideal fir héich performant elektronesch Apparater.

4H-SiC PolytypDe 4H-SiC Polytyp ass bekannt fir seng héich Effizienz a Stabilitéit an elektroneschen Uwendungen.

N-Typ DopingN-Typ Dotierung (mat Stéckstoff dotiert) bitt eng exzellent Elektronemobilitéit, wouduerch SiC fir Héichfrequenz- an Héichleistungsapplikatioune gëeegent ass.

Héich thermesch Konduktivitéit:

SiC-Wafers hunn eng iwwerleeën Wärmeleitfäegkeet, typescherweis tëscht120–200 W/m·K, wat hinnen erlaabt, d'Hëtzt an Héichleistungsgeräter wéi Transistoren an Dioden effektiv ze verwalten.

Breet Bandlück:

Mat enger Bandlück vun3,26 eV, 4H-SiC kann am Verglach mat traditionellen Silizium-baséierten Apparater bei méi héije Spannungen, Frequenzen an Temperaturen funktionéieren, wat et ideal fir héicheffizient an héichperformant Uwendungen mécht.

Elektresch Eegeschaften:

Déi héich Elektronemobilitéit a Konduktivitéit vu SiC maachen et ideal firLeeschtungselektronik, déi séier Schaltgeschwindegkeeten an eng héich Stroum- a Spannungskapazitéit ubidden, wat zu méi effiziente Stroummanagementsystemer féiert.

Mechanesch a chemesch Resistenz:

SiC ass ee vun den härtesten Materialien, nëmmen no Diamant déi zweethärtegst, an ass héich resistent géint Oxidatioun a Korrosioun, wouduerch et och an haarden Ëmfeld haltbar ass.

Uwendungen vun SiC 4H-N Typ Epi Wafer:

Leeschtungselektronik:

Epi-Wafere vum Typ SiC 4H-N gi wäit verbreet aPower MOSFETs, IGBTs, anDiodenfirEnergiekonversiouna Systemer wéi z.B.Solarinverter, elektresch Gefierer, anEnergiespeichersystemer, wat eng verbessert Leeschtung an Energieeffizienz bitt.

Elektroautoen (EVs):

In Undriffssystemer fir elektresch Gefierer, Motorregler, anOpluedstatiounen, SiC-Waferen hëllefen eng besser Batterieeffizienz, méi séier Laden an eng verbessert allgemeng Energieleistung z'erreechen, well se géint héich Leeschtung an Temperaturen fäeg sinn.

Erneierbar Energiesystemer:

SolarinverterSiC-Wafere ginn agesatSolarenergiesystemerfir d'Ëmwandlung vun der Gläichstroumversuergung vu Solarpanneauen an Wiesselstroum, wat d'Gesamteffizienz an d'Leeschtung vum System erhéicht.

WandturbinnenSiC-Technologie gëtt agesatWandturbinnenkontrollsystemer, Optimiséierung vun der Energieerzeugung an der Konversiounseffizienz.

Loft- a Raumfaart a Verdeedegung:

SiC-Wafers si perfekt fir d'Benotzung anLoftfaart-Elektronikanmilitäresch Uwendungen, dorënnerRadarsystemeranSatellittenelektronik, wou eng héich Stralungsbeständegkeet an thermesch Stabilitéit entscheedend sinn.

Héichtemperatur- an Héichfrequenzapplikatiounen:

SiC-Wafers exceléieren anHéichtemperaturelektronik, benotzt anFligermotoren, Raumschëff, anindustriell Heizungssystemer, well se hir Leeschtung bei extremen Hëtztbedingungen behalen. Zousätzlech erlaabt hir grouss Bandlück d'Benotzung anHéichfrequenzapplikatiounenwéiRF-GeräteranMikrowellenkommunikatioun.

| 6-Zoll N-Typ Epit Axial Spezifikatioun | |||

| Parameter | Eenheet | Z-MOS | |

| Typ | Konduktivitéit / Dotierstoff | - | N-Typ / Stéckstoff |

| Pufferschicht | Déckt vun der Pufferschicht | um | 1 |

| Toleranz vun der Pufferschichtdicke | % | ±20% | |

| Konzentratioun vun der Pufferschicht | cm-3 | 1.00E+18 | |

| Konzentratiounstoleranz vun der Pufferschicht | % | ±20% | |

| 1. Epi-Schicht | Epi-Schichtdicke | um | 11,5 |

| Epi-Schichtdicke-Uniformitéit | % | ±4% | |

| Epi-Schichten Dicke Toleranz ((Spezifikatioun- Max, Min)/Spezifikatioun) | % | ±5% | |

| Epi-Schichtkonzentratioun | cm-3 | 1. E. 15~ 1. E. 18 | |

| Epi-Schicht Konzentratiounstoleranz | % | 6% | |

| Epi-Schicht-Konzentratiounsuniformitéit (σ) /bedeiten) | % | ≤5% | |

| Epi-Schicht Konzentratiounsuniformitéit <(max-min)/(max+min> | % | ≤ 10% | |

| Epitaixal Waferform | Béi | um | ≤±20 |

| WARP | um | ≤30 | |

| TTV | um | ≤ 10 | |

| LTV | um | ≤2 | |

| Allgemeng Charakteristiken | Kratzerlängt | mm | ≤30mm |

| Kantchips | - | KEEN | |

| Definitioun vu Mängel | ≥97% (Gemooss mat 2*2, Killer Defekter enthalen: Defekter enthalen Mikropäif / Grouss Kären, Muert, Dräieckeg | ||

| Metallkontaminatioun | Atomer/cm² | d f f ll i ≤5E10 Atomer/cm2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca & Mn) | |

| Pak | Verpackungsspezifikatiounen | Stéck/Këscht | Multi-Wafer-Kassett oder Eenzel-Wafer-Behälter |

| 8-Zoll N-Typ epitaktesch Spezifikatioun | |||

| Parameter | Eenheet | Z-MOS | |

| Typ | Konduktivitéit / Dotierstoff | - | N-Typ / Stéckstoff |

| Pufferschicht | Déckt vun der Pufferschicht | um | 1 |

| Toleranz vun der Pufferschichtdicke | % | ±20% | |

| Konzentratioun vun der Pufferschicht | cm-3 | 1.00E+18 | |

| Konzentratiounstoleranz vun der Pufferschicht | % | ±20% | |

| 1. Epi-Schicht | Duerchschnëttlech Dicke vun den Epi-Schichten | um | 8~ 12 |

| Epi-Schichten-Décktuniformitéit (σ/Moyenne) | % | ≤2.0 | |

| Epi-Schichten Dicke Toleranz ((Spec -Max, Min) / Spez) | % | ±6 | |

| Duerchschnëttlech Doping vun Epi-Schichten | cm-3 | 8E+15 ~2E+16 | |

| Epi-Schichten Netto-Dopinguniformitéit (σ/Moyenne) | % | ≤5 | |

| Epi Schichten Netto Doping Toleranz ((Spec -Max, | % | ± 10,0 | |

| Epitaixal Waferform | Mi )/S ) Ketten | um | ≤50,0 |

| Béi | um | ± 30,0 | |

| TTV | um | ≤ 10,0 | |

| LTV | um | ≤4,0 (10 mm × 10 mm) | |

| Allgemeng Charakteristiken | Kratzer | - | Kumulativ Längt ≤ 1/2 Wafer Duerchmiesser |

| Kantchips | - | ≤2 Chips, all Radius ≤1.5mm | |

| Kontaminatioun vu Metaller op der Uewerfläch | Atomer/cm² | ≤5E10 Atomer/cm2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca & Mn) | |

| Defektinspektioun | % | ≥ 96,0 (2X2 Defekter enthalen Mikropäif / Grouss Lächer, Muert, Dräieckeg Defekter, Nodeeler, Linear/IGSF-en, BPD) | |

| Kontaminatioun vu Metaller op der Uewerfläch | Atomer/cm² | ≤5E10 Atomer/cm2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca & Mn) | |

| Pak | Verpackungsspezifikatiounen | - | Multi-Wafer-Kassett oder Eenzel-Wafer-Behälter |

Froen an Äntwerten iwwer SiC-Waferen

Q1: Wat sinn déi wichtegst Virdeeler vun der Verwendung vu SiC-Wafers am Verglach mat traditionelle Siliziumwafers an der Leeschtungselektronik?

A1:

SiC-Waferen bidden e puer Schlësselvirdeeler géintiwwer traditionelle Silizium (Si)-Waferen an der Leeschtungselektronik, dorënner:

Méi héich EffizienzSiC huet eng méi grouss Bandlück (3,26 eV) am Verglach mat Silizium (1,1 eV), wat et den Apparater erlaabt, bei méi héije Spannungen, Frequenzen an Temperaturen ze funktionéieren. Dëst féiert zu engem méi niddrege Stroumverloscht an enger méi héijer Effizienz a Stroumkonversiounssystemer.

Héich thermesch KonduktivitéitD'Wärmeleitfäegkeet vu SiC ass vill méi héich wéi déi vu Silizium, wat eng besser Wärmeofleedung an Uwendungen mat héijer Leeschtung erméiglecht, wat d'Zouverlässegkeet an d'Liewensdauer vu Stroumversuergungsapparater verbessert.

Ëmgang mat méi héijer Spannung a StroumSiC-Apparater kënne méi héich Spannungs- a Stroumniveauen handhaben, wouduerch se fir Uwendungen mat héijer Leeschtung wéi Elektroautoen, erneierbar Energiesystemer an industriell Motorundriff gëeegent sinn.

Méi séier SchaltgeschwindegkeetSiC-Komponente hunn méi séier Schaltméiglechkeeten, déi zu enger Reduktioun vum Energieverloscht a vun der Systemgréisst bäidroen, wouduerch se ideal fir Héichfrequenzapplikatioune sinn.

Q2: Wat sinn déi wichtegst Uwendungen vu SiC-Waferen an der Automobilindustrie?

A2:

An der Automobilindustrie ginn SiC-Waferen haaptsächlech an:

Undriffssystemer fir Elektroautoen (EV)Komponenten op Basis vu SiC, wéi zum BeispillInverteranPower MOSFETsd'Effizienz an d'Leeschtung vun Elektroauto-Undriffssystemer verbesseren andeems méi séier Schaltgeschwindegkeeten an eng méi héich Energiedicht erméiglecht ginn. Dëst féiert zu enger méi laanger Batterielaufzäit an enger besserer Gesamtleeschtung vum Gefier.

Ladegeräter u BordSiC-Apparater hëllefen d'Effizienz vun agebaute Ladesystemer ze verbesseren, andeems se méi séier Ladezäiten an e bessert Wärmemanagement erméiglechen, wat entscheedend ass fir Elektroautoen, fir Héichleistungs-Ladestatiounen z'ënnerstëtzen.

Batteriemanagementsystemer (BMS)SiC-Technologie verbessert d'Effizienz vunBatteriemanagementsystemer, wat eng besser Spannungsreguléierung, eng méi héich Leeschtungsveraarbechtung a méi laang Batterielaufzäit erméiglecht.

Gläichstroum-Gläichstroum-KonverterSiC-Wafere ginn agesatDC-DC Konverterfir Héichspannungs-Gläichstroum méi effizient an Nidderspannungs-Gläichstroum ëmzewandelen, wat bei Elektroautoen entscheedend ass, fir d'Stroumversuergung vun der Batterie zu verschiddene Komponenten am Gefier ze verwalten.

Déi iwwerleeën Leeschtung vu SiC a Héichspannungs-, Héichtemperatur- an Héicheffizienzuwendungen mécht et essentiell fir den Iwwergank vun der Automobilindustrie op d'Elektromobilitéit.

Spezifikatioun vun 6 Zoll 4H-N Typ SiC Wafer | ||

| Immobilie | Null MPD Produktiounsgrad (Z-Grad) | Dummy-Klass (Klass D) |

| Grad | Null MPD Produktiounsgrad (Z-Grad) | Dummy-Klass (Klass D) |

| Duerchmiesser | 149,5 mm – 150,0 mm | 149,5 mm – 150,0 mm |

| Poly-Typ | 4H | 4H |

| Déckt | 350 µm ± 15 µm | 350 µm ± 25 µm |

| Wafer Orientéierung | Off-axis: 4,0° Richtung <1120> ± 0,5° | Off-axis: 4,0° Richtung <1120> ± 0,5° |

| Mikropäifdicht | ≤ 0,2 cm² | ≤ 15 cm² |

| Widderstandsfäegkeet | 0,015 – 0,024 Ω·cm | 0,015 – 0,028 Ω·cm |

| Primär flaach Orientéierung | [10-10] ± 50° | [10-10] ± 50° |

| Primär flaach Längt | 475 mm ± 2,0 mm | 475 mm ± 2,0 mm |

| Randausgrenzung | 3 mm | 3 mm |

| LTV/TIV / Béi / Ketten | ≤ 2,5 µm / ≤ 6 µm / ≤ 25 µm / ≤ 35 µm | ≤ 5 µm / ≤ 15 µm / ≤ 40 µm / ≤ 60 µm |

| Rauheet | Polnesch Ra ≤ 1 nm | Polnesch Ra ≤ 1 nm |

| CMP Ra | ≤ 0,2 nm | ≤ 0,5 nm |

| Kantrëss duerch héichintensivt Liicht | Kumulativ Längt ≤ 20 mm, eenzel Längt ≤ 2 mm | Kumulativ Längt ≤ 20 mm, eenzel Längt ≤ 2 mm |

| Sechseckplacken duerch héichintensivt Liicht | Kumulativ Fläch ≤ 0,05% | Kumulativ Fläch ≤ 0,1% |

| Polytypberäicher duerch héichintensivt Liicht | Kumulativ Fläch ≤ 0,05% | Kumulativ Fläch ≤ 3% |

| Visuell Kuelestoffinklusiounen | Kumulativ Fläch ≤ 0,05% | Kumulativ Fläch ≤ 5% |

| Siliziumoberfläche kraazt duerch héichintensivt Liicht | Kumulativ Längt ≤ 1 Waferduerchmiesser | |

| Kantchips duerch héichintensivt Liicht | Keen erlaabt ≥ 0,2 mm Breet an Déift | 7 erlaabt, ≤ 1 mm all |

| Verrécklung vun der Gewënnschraube | < 500 cm³ | < 500 cm³ |

| Kontaminatioun vun der Siliziumoberfläche duerch héichintensivt Liicht | ||

| Verpackung | Multi-Wafer Kassett oder Eenzelwafer Behälter | Multi-Wafer Kassett oder Eenzelwafer Behälter |

Spezifikatioun vun 8 Zoll 4H-N Typ SiC Wafer | ||

| Immobilie | Null MPD Produktiounsgrad (Z-Grad) | Dummy-Klass (Klass D) |

| Grad | Null MPD Produktiounsgrad (Z-Grad) | Dummy-Klass (Klass D) |

| Duerchmiesser | 199,5 mm – 200,0 mm | 199,5 mm – 200,0 mm |

| Poly-Typ | 4H | 4H |

| Déckt | 500 µm ± 25 µm | 500 µm ± 25 µm |

| Wafer Orientéierung | 4,0° Richtung <110> ± 0,5° | 4,0° Richtung <110> ± 0,5° |

| Mikropäifdicht | ≤ 0,2 cm² | ≤ 5 cm² |

| Widderstandsfäegkeet | 0,015 – 0,025 Ω·cm | 0,015 – 0,028 Ω·cm |

| Edel Orientéierung | ||

| Randausgrenzung | 3 mm | 3 mm |

| LTV/TIV / Béi / Ketten | ≤ 5 µm / ≤ 15 µm / ≤ 35 µm / 70 µm | ≤ 5 µm / ≤ 15 µm / ≤ 35 µm / 100 µm |

| Rauheet | Polnesch Ra ≤ 1 nm | Polnesch Ra ≤ 1 nm |

| CMP Ra | ≤ 0,2 nm | ≤ 0,5 nm |

| Kantrëss duerch héichintensivt Liicht | Kumulativ Längt ≤ 20 mm, eenzel Längt ≤ 2 mm | Kumulativ Längt ≤ 20 mm, eenzel Längt ≤ 2 mm |

| Sechseckplacken duerch héichintensivt Liicht | Kumulativ Fläch ≤ 0,05% | Kumulativ Fläch ≤ 0,1% |

| Polytypberäicher duerch héichintensivt Liicht | Kumulativ Fläch ≤ 0,05% | Kumulativ Fläch ≤ 3% |

| Visuell Kuelestoffinklusiounen | Kumulativ Fläch ≤ 0,05% | Kumulativ Fläch ≤ 5% |

| Siliziumoberfläche kraazt duerch héichintensivt Liicht | Kumulativ Längt ≤ 1 Waferduerchmiesser | |

| Kantchips duerch héichintensivt Liicht | Keen erlaabt ≥ 0,2 mm Breet an Déift | 7 erlaabt, ≤ 1 mm all |

| Verrécklung vun der Gewënnschraube | < 500 cm³ | < 500 cm³ |

| Kontaminatioun vun der Siliziumoberfläche duerch héichintensivt Liicht | ||

| Verpackung | Multi-Wafer Kassett oder Eenzelwafer Behälter | Multi-Wafer Kassett oder Eenzelwafer Behälter |

Spezifikatioun vum 6 Zoll 4H-Semi-SiC-Substrat | ||

| Immobilie | Null MPD Produktiounsgrad (Z-Grad) | Dummy-Klass (Klass D) |

| Duerchmiesser (mm) | 145 mm – 150 mm | 145 mm – 150 mm |

| Poly-Typ | 4H | 4H |

| Déckt (um) | 500 ± 15 | 500 ± 25 |

| Wafer Orientéierung | Op der Achs: ±0,0001° | Op der Achs: ±0,05° |

| Mikropäifdicht | ≤ 15 cm-2 | ≤ 15 cm-2 |

| Widderstand (Ωcm) | ≥ 10E3 | ≥ 10E3 |

| Primär flaach Orientéierung | (0-10)° ± 5,0° | (10-10)° ± 5,0° |

| Primär flaach Längt | Kerb | Kerb |

| Kantenausgrenzung (mm) | ≤ 2,5 µm / ≤ 15 µm | ≤ 5,5 µm / ≤ 35 µm |

| LTV / Schossel / Warp | ≤ 3 µm | ≤ 3 µm |

| Rauheet | Poléiert Ra ≤ 1,5 µm | Poléiert Ra ≤ 1,5 µm |

| Kantchips duerch héichintensivt Liicht | ≤ 20 µm | ≤ 60 µm |

| Hëtztplacken duerch héichintensivt Liicht | Kumulativ ≤ 0,05% | Kumulativ ≤ 3% |

| Polytypberäicher duerch héichintensivt Liicht | Visuell Kuelestoffinklusiounen ≤ 0,05% | Kumulativ ≤ 3% |

| Siliziumoberfläche kraazt duerch héichintensivt Liicht | ≤ 0,05% | Kumulativ ≤ 4% |

| Kantchips duerch héichintensivt Liicht (Gréisst) | Net erlaabt > 02 mm Breet an Déift | Net erlaabt > 02 mm Breet an Déift |

| D'Hëllefsschraufdilatatioun | ≤ 500 µm | ≤ 500 µm |

| Kontaminatioun vun der Siliziumoberfläche duerch héichintensivt Liicht | ≤ 1 x 10^5 | ≤ 1 x 10^5 |

| Verpackung | Multi-Wafer-Kassett oder Eenzelwafer-Behälter | Multi-Wafer-Kassett oder Eenzelwafer-Behälter |

Spezifikatioun vum 4-Zoll 4H-Halbisoléierende SiC-Substrat

| Parameter | Null MPD Produktiounsgrad (Z-Grad) | Dummy-Klass (Klass D) |

|---|---|---|

| Physikalesch Eegeschaften | ||

| Duerchmiesser | 99,5 mm – 100,0 mm | 99,5 mm – 100,0 mm |

| Poly-Typ | 4H | 4H |

| Déckt | 500 μm ± 15 μm | 500 μm ± 25 μm |

| Wafer Orientéierung | Op der Achs: <600h > 0,5° | Op der Achs: <000h > 0,5° |

| Elektresch Eegeschaften | ||

| Mikropäifdicht (MPD) | ≤1 cm⁻² | ≤15 cm⁻² |

| Widderstandsfäegkeet | ≥150 Ω·cm | ≥1,5 Ω·cm |

| Geometresch Toleranzen | ||

| Primär flaach Orientéierung | (0×10) ± 5,0° | (0×10) ± 5,0° |

| Primär flaach Längt | 52,5 mm ± 2,0 mm | 52,5 mm ± 2,0 mm |

| Sekundär flaach Längt | 18,0 mm ± 2,0 mm | 18,0 mm ± 2,0 mm |

| Sekundär flaach Orientéierung | 90° mat der rietser Säit vun der Prime-Flaach ± 5,0° (Si-Front no uewen) | 90° mat der rietser Säit vun der Prime-Flaach ± 5,0° (Si-Front no uewen) |

| Randausgrenzung | 3 mm | 3 mm |

| LTV / TTV / Béi / Ketten | ≤2,5 μm / ≤5 μm / ≤15 μm / ≤30 μm | ≤10 μm / ≤15 μm / ≤25 μm / ≤40 μm |

| Uewerflächenqualitéit | ||

| Uewerflächenrauheet (Polnesch Ra) | ≤1 nm | ≤1 nm |

| Uewerflächenrauheet (CMP Ra) | ≤0,2 nm | ≤0,2 nm |

| Rëss um Rand (Héichintensivt Liicht) | Net erlaabt | Kumulativ Längt ≥10 mm, eenzel Rëss ≤2 mm |

| Defekter vun der sechseckeger Placke | ≤0,05% kumulativ Fläch | ≤0,1% kumulativ Fläch |

| Polytyp-Inklusiounsgebidder | Net erlaabt | ≤1% kumulativ Fläch |

| Visuell Kuelestoffinklusiounen | ≤0,05% kumulativ Fläch | ≤1% kumulativ Fläch |

| Kratzer op der Silikonoberfläche | Net erlaabt | Kumulativ Längt vun ≤1 Waferduerchmiesser |

| Kantchips | Net erlaabt (≥0,2 mm Breet/Déift) | ≤5 Chips (jeeweils ≤1 mm) |

| Kontaminatioun vun der Siliziumoberfläche | Net spezifizéiert | Net spezifizéiert |

| Verpackung | ||

| Verpackung | Multi-Wafer-Kassett oder Eenzel-Wafer-Behälter | Multi-Wafer-Kassett oder |

| 6-Zoll N-Typ Epit Axial Spezifikatioun | |||

| Parameter | Eenheet | Z-MOS | |

| Typ | Konduktivitéit / Dotierstoff | - | N-Typ / Stéckstoff |

| Pufferschicht | Déckt vun der Pufferschicht | um | 1 |

| Toleranz vun der Pufferschichtdicke | % | ±20% | |

| Konzentratioun vun der Pufferschicht | cm-3 | 1.00E+18 | |

| Konzentratiounstoleranz vun der Pufferschicht | % | ±20% | |

| 1. Epi-Schicht | Epi-Schichtdicke | um | 11,5 |

| Epi-Schichtdicke-Uniformitéit | % | ±4% | |

| Epi-Schichten Dicke Toleranz ((Spezifikatioun- Max, Min)/Spezifikatioun) | % | ±5% | |

| Epi-Schichtkonzentratioun | cm-3 | 1. E. 15~ 1. E. 18 | |

| Epi-Schicht Konzentratiounstoleranz | % | 6% | |

| Epi-Schicht-Konzentratiounsuniformitéit (σ) /bedeiten) | % | ≤5% | |

| Epi-Schicht Konzentratiounsuniformitéit <(max-min)/(max+min> | % | ≤ 10% | |

| Epitaixal Waferform | Béi | um | ≤±20 |

| WARP | um | ≤30 | |

| TTV | um | ≤ 10 | |

| LTV | um | ≤2 | |

| Allgemeng Charakteristiken | Kratzerlängt | mm | ≤30mm |

| Kantchips | - | KEEN | |

| Definitioun vu Mängel | ≥97% (Gemooss mat 2*2, Killer Defekter enthalen: Defekter enthalen Mikropäif / Grouss Kären, Muert, Dräieckeg | ||

| Metallkontaminatioun | Atomer/cm² | d f f ll i ≤5E10 Atomer/cm2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca & Mn) | |

| Pak | Verpackungsspezifikatiounen | Stéck/Këscht | Multi-Wafer-Kassett oder Eenzel-Wafer-Behälter |

| 8-Zoll N-Typ epitaktesch Spezifikatioun | |||

| Parameter | Eenheet | Z-MOS | |

| Typ | Konduktivitéit / Dotierstoff | - | N-Typ / Stéckstoff |

| Pufferschicht | Déckt vun der Pufferschicht | um | 1 |

| Toleranz vun der Pufferschichtdicke | % | ±20% | |

| Konzentratioun vun der Pufferschicht | cm-3 | 1.00E+18 | |

| Konzentratiounstoleranz vun der Pufferschicht | % | ±20% | |

| 1. Epi-Schicht | Duerchschnëttlech Dicke vun den Epi-Schichten | um | 8~ 12 |

| Epi-Schichten-Décktuniformitéit (σ/Moyenne) | % | ≤2.0 | |

| Epi-Schichten Dicke Toleranz ((Spec -Max, Min) / Spez) | % | ±6 | |

| Duerchschnëttlech Doping vun Epi-Schichten | cm-3 | 8E+15 ~2E+16 | |

| Epi-Schichten Netto-Dopinguniformitéit (σ/Moyenne) | % | ≤5 | |

| Epi Schichten Netto Doping Toleranz ((Spec -Max, | % | ± 10,0 | |

| Epitaixal Waferform | Mi )/S ) Ketten | um | ≤50,0 |

| Béi | um | ± 30,0 | |

| TTV | um | ≤ 10,0 | |

| LTV | um | ≤4,0 (10 mm × 10 mm) | |

| Allgemeng Charakteristiken | Kratzer | - | Kumulativ Längt ≤ 1/2 Wafer Duerchmiesser |

| Kantchips | - | ≤2 Chips, all Radius ≤1.5mm | |

| Kontaminatioun vu Metaller op der Uewerfläch | Atomer/cm² | ≤5E10 Atomer/cm2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca & Mn) | |

| Defektinspektioun | % | ≥ 96,0 (2X2 Defekter enthalen Mikropäif / Grouss Lächer, Muert, Dräieckeg Defekter, Nodeeler, Linear/IGSF-en, BPD) | |

| Kontaminatioun vu Metaller op der Uewerfläch | Atomer/cm² | ≤5E10 Atomer/cm2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca & Mn) | |

| Pak | Verpackungsspezifikatiounen | - | Multi-Wafer-Kassett oder Eenzel-Wafer-Behälter |

Q1: Wat sinn déi wichtegst Virdeeler vun der Verwendung vu SiC-Wafers am Verglach mat traditionelle Siliziumwafers an der Leeschtungselektronik?

A1:

SiC-Waferen bidden e puer Schlësselvirdeeler géintiwwer traditionelle Silizium (Si)-Waferen an der Leeschtungselektronik, dorënner:

Méi héich EffizienzSiC huet eng méi grouss Bandlück (3,26 eV) am Verglach mat Silizium (1,1 eV), wat et den Apparater erlaabt, bei méi héije Spannungen, Frequenzen an Temperaturen ze funktionéieren. Dëst féiert zu engem méi niddrege Stroumverloscht an enger méi héijer Effizienz a Stroumkonversiounssystemer.

Héich thermesch KonduktivitéitD'Wärmeleitfäegkeet vu SiC ass vill méi héich wéi déi vu Silizium, wat eng besser Wärmeofleedung an Uwendungen mat héijer Leeschtung erméiglecht, wat d'Zouverlässegkeet an d'Liewensdauer vu Stroumversuergungsapparater verbessert.

Ëmgang mat méi héijer Spannung a StroumSiC-Apparater kënne méi héich Spannungs- a Stroumniveauen handhaben, wouduerch se fir Uwendungen mat héijer Leeschtung wéi Elektroautoen, erneierbar Energiesystemer an industriell Motorundriff gëeegent sinn.

Méi séier SchaltgeschwindegkeetSiC-Komponente hunn méi séier Schaltméiglechkeeten, déi zu enger Reduktioun vum Energieverloscht a vun der Systemgréisst bäidroen, wouduerch se ideal fir Héichfrequenzapplikatioune sinn.

Q2: Wat sinn déi wichtegst Uwendungen vu SiC-Waferen an der Automobilindustrie?

A2:

An der Automobilindustrie ginn SiC-Waferen haaptsächlech an:

Undriffssystemer fir Elektroautoen (EV)Komponenten op Basis vu SiC, wéi zum BeispillInverteranPower MOSFETsd'Effizienz an d'Leeschtung vun Elektroauto-Undriffssystemer verbesseren andeems méi séier Schaltgeschwindegkeeten an eng méi héich Energiedicht erméiglecht ginn. Dëst féiert zu enger méi laanger Batterielaufzäit an enger besserer Gesamtleeschtung vum Gefier.

Ladegeräter u BordSiC-Apparater hëllefen d'Effizienz vun agebaute Ladesystemer ze verbesseren, andeems se méi séier Ladezäiten an e bessert Wärmemanagement erméiglechen, wat entscheedend ass fir Elektroautoen, fir Héichleistungs-Ladestatiounen z'ënnerstëtzen.

Batteriemanagementsystemer (BMS)SiC-Technologie verbessert d'Effizienz vunBatteriemanagementsystemer, wat eng besser Spannungsreguléierung, eng méi héich Leeschtungsveraarbechtung a méi laang Batterielaufzäit erméiglecht.

Gläichstroum-Gläichstroum-KonverterSiC-Wafere ginn agesatDC-DC Konverterfir Héichspannungs-Gläichstroum méi effizient an Nidderspannungs-Gläichstroum ëmzewandelen, wat bei Elektroautoen entscheedend ass, fir d'Stroumversuergung vun der Batterie zu verschiddene Komponenten am Gefier ze verwalten.

Déi iwwerleeën Leeschtung vu SiC a Héichspannungs-, Héichtemperatur- an Héicheffizienzuwendungen mécht et essentiell fir den Iwwergank vun der Automobilindustrie op d'Elektromobilitéit.