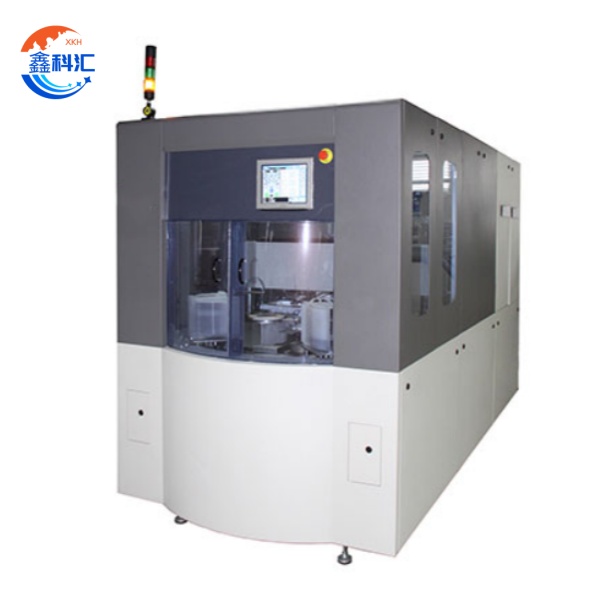

Waferverdënnungsausrüstung fir d'Veraarbechtung vu Saphir/SiC/Si-Wafelen vun 4-12 Zoll

Aarbechtsprinzip

De Prozess vun der Waferverdënnung funktionéiert a dräi Etappen:

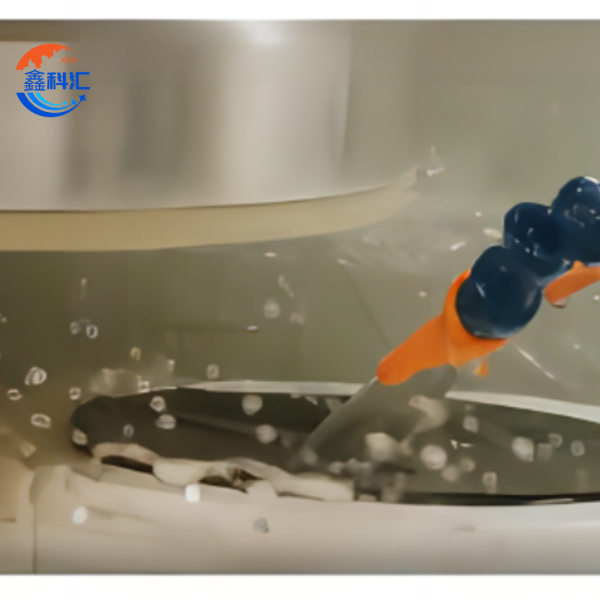

Grobschleifen: Eng Diamantscheif (Korngréisst 200–500 μm) läscht 50–150 μm Material bei 3000–5000 U/min, fir d'Dicke séier ze reduzéieren.

Feinschleifen: Eng méi fein Scheif (Korngréisst 1–50 μm) reduzéiert d'Déckt op 20–50 μm bei <1 μm/s, fir Schied un der Ënnerfläch ze minimiséieren.

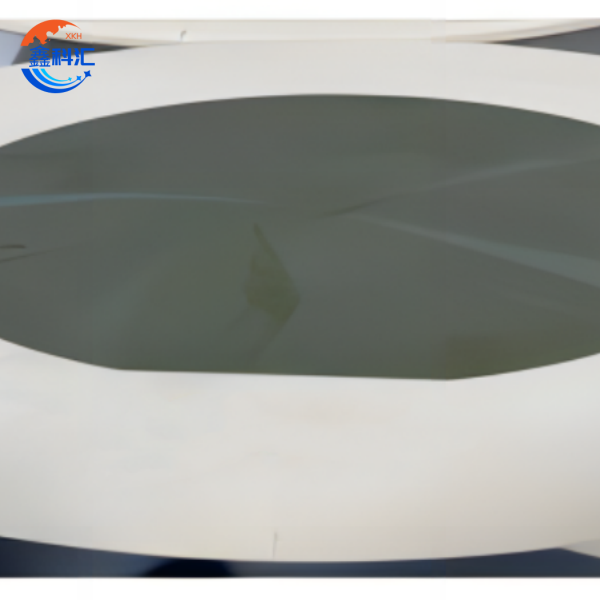

Poléieren (CMP): E chemesch-mechanesche Schläim eliminéiert Reschtschued a erreecht e Ra <0,1 nm.

Kompatibel Materialien

Silizium (Si): Standard fir CMOS-Waferen, verdënnt op 25 μm fir 3D-Stacking.

Siliziumkarbid (SiC): Erfuerdert speziell Diamantscheiwen (80% Diamantkonzentratioun) fir thermesch Stabilitéit.

Saphir (Al₂O₃): Verdënnt op 50 μm fir UV-LED-Uwendungen.

Kär Systemkomponenten

1. Schleifsystem

Duebelachseschleifmaschinn: Kombinéiert Grob-/Feinschleifen op enger eenzeger Plattform, reduzéiert d'Zykluszäit ëm 40%.

Aerostatesch Spindel: Drehzahlberäich vun 0–6000 U/min mat engem radialen Auslaf vun <0,5 μm.

2. Wafer-Handhabungssystem

Vakuumfutter: >50 N Haltkraaft mat ±0,1 μm Positionéierungsgenauegkeet.

Roboterarm: Transportéiert 4–12-Zoll-Waferen mat 100 mm/s.

3. Kontrollsystem

Laserinterferometrie: Echtzäit-Déckteniwwerwaachung (Opléisung 0,01 μm).

KI-gedriwwenen Feedforward: Viraussoe vum Radverschleiung a passt d'Parameteren automatesch un.

4. Ofkillen & Botzen

Ultraschallreinigung: Entfernt Partikelen >0,5 μm mat 99,9% Effizienz.

Deioniséiert Waasser: Killt d'Wafer op <5°C iwwer der Ëmgéigungstemperatur of.

Kärvirdeeler

1. Ultrahéich Präzisioun: TTV (Total Dickness Variation) <0,5 μm, WTW (Within-Wafer Dickness Variation) <1 μm.

2. Multi-Prozess Integratioun: Kombinéiert Schleifen, CMP a Plasmaätzen an enger Maschinn.

3. Materialkompatibilitéit:

Silizium: Décktereduktioun vu 775 μm op 25 μm.

SiC: Erreecht <2 μm TTV fir RF-Uwendungen.

Dotiert Waferen: Phosphor-dotiert InP-Waferen mat enger Widderstandsdrift vun <5%.

4. Smart Automation: MES-Integratioun reduzéiert mënschlech Feeler ëm 70%.

5. Energieeffizienz: 30% méi niddrege Stroumverbrauch duerch regenerativ Bremsen.

Schlësselapplikatiounen

1. Fortgeschratt Verpackung

• 3D-ICs: Wafer-Verdënnung erméiglecht vertikal Stacking vu Logik-/Speicherchips (z.B. HBM-Stacks), wouduerch eng 10x méi héich Bandbreet an e 50% reduzéierte Stroumverbrauch am Verglach mat 2,5D-Léisunge erreecht gëtt. D'Ausrüstung ënnerstëtzt Hybrid Bonding an TSV-Integratioun (Through-Silicon Via), wat entscheedend ass fir KI/ML-Prozessoren, déi eng Interconnect-Pitch vun <10 μm brauchen. Zum Beispill erlaben 12-Zoll-Wafers, déi op 25 μm verdënnt sinn, d'Stapelung vun 8+ Schichten, während d'Verzerrung vun <1,5% behalen gëtt, wat essentiell fir LiDAR-Systemer am Automobilberäich ass.

• Fan-Out Packaging: Duerch d'Reduktioun vun der Waferdicke op 30 μm gëtt d'Verbindungslängt ëm 50% verkierzt, wouduerch d'Signalverzögerung (<0,2 ps/mm) miniméiert gëtt an 0,4 mm ultradënn Chiplets fir mobil SoCs erméiglecht ginn. De Prozess notzt stresskompenséiert Schleifalgorithmen fir Verzerrung ze vermeiden (>50 μm TTV-Kontroll), wat Zouverlässegkeet an Héichfrequenz-HF-Applikatiounen garantéiert.

2. Leeschtungselektronik

• IGBT-Moduler: Verdënnung op 50 μm reduzéiert den thermesche Widderstand op <0,5°C/W, wouduerch 1200V SiC-MOSFETs bei Junctiontemperature vun 200°C funktionéiere kënnen. Eis Ausrüstung benotzt e Méistufeschleifen (grov: 46 μm Grit → fein: 4 μm Grit) fir Schied un der Ënnerfläch ze eliminéieren, wouduerch >10.000 Zyklen vun thermescher Zykliséierungszouverlässegkeet erreecht ginn. Dëst ass entscheedend fir EV-Inverter, wou 10 μm déck SiC-Waferen d'Schaltgeschwindegkeet ëm 30% verbesseren.

• GaN-op-SiC-Energieversuergungskomponenten: Waferverdënnung op 80 μm verbessert d'Elektronemobilitéit (μ > 2000 cm²/V·s) fir 650V GaN HEMTs, wouduerch d'Leetungsverloschter ëm 18% reduzéiert ginn. De Prozess benotzt lasergestëtzt Dicing, fir Rëssbildung beim Verdënnen ze vermeiden, wouduerch <5 μm Kantenabsplittung fir HF-Energieverstärker erreecht gëtt.

3. Optoelektronik

• GaN-op-SiC LEDs: 50 μm Saphirsubstrate verbesseren d'Liichtextraktiounseffizienz (LEE) op 85% (am Verglach zu 65% fir 150 μm Waferen) andeems se d'Photonenfange miniméieren. Déi ultra-niddreg TTV-Kontroll vun eiser Ausrüstung (<0,3 μm) garantéiert eng eenheetlech LED-Emissioun iwwer 12-Zoll-Waferen, wat entscheedend ass fir Micro-LED-Displays, déi eng Wellelängteuniformitéit vu <100nm erfuerderen.

• Siliziumphotonik: 25 μm déck Siliziumwafer erméiglechen 3 dB/cm méi niddrege Propagatiounsverloscht a Wellenleiter, essentiell fir 1,6 Tbps optesch Transceiver. De Prozess integréiert CMP-Glättung fir d'Uewerflächenrauheet op Ra <0,1 nm ze reduzéieren, wat d'Kopplungseffizienz ëm 40% erhéicht.

4. MEMS-Sensoren

• Beschleunigungsmesser: 25 μm Siliziumwafer erreechen eng Signal-Rausch ...

• Drocksensoren: Verdënnung op 40 μm erméiglecht Miessberäicher vun 0–300 bar mat enger Hysterese vu manner wéi 0,1% FS. Mat temporärer Bindung (Glasträger) vermeit de Prozess Waferfraktur beim Réckseiteätzungen, wouduerch eng Iwwerdrocktoleranz vu manner wéi 1 μm fir industriell IoT-Sensoren erreecht gëtt.

• Technesch Synergie: Eis Waferverdënnungsausrüstung vereenegt mechanescht Schleifen, CMP a Plasmaätzen, fir verschidde Materialproblemer (Si, SiC, Saphir) unzegoen. Zum Beispill erfuerdert GaN-op-SiC en Hybridschleifen (Diamantrieder + Plasma) fir d'Häert an d'thermesch Expansioun auszebalancéieren, während MEMS-Sensoren eng Uewerflächenrauheet vu manner wéi 5 nm iwwer CMP-Poléieren erfuerderen.

• Impakt op d'Industrie: Duerch d'Erméiglechkeet vun méi dënne, méi performante Waferen, féiert dës Technologie zu Innovatiounen an KI-Chips, 5G mmWave-Moduler a flexibeler Elektronik, mat TTV-Toleranzen <0,1 μm fir klappbar Displays an <0,5 μm fir LiDAR-Sensoren am Automobilberäich.

D'Servicer vun XKH

1. Personaliséiert Léisungen

Skalierbar Konfiguratiounen: Kammerdesignen vun 4–12 Zoll mat automatiséiertem Belueden/Entlueden.

Dopingënnerstëtzung: Benotzerdefinéiert Rezepter fir Er/Yb-dotiert Kristaller an InP/GaAs-Waferen.

2. End-to-End Support

Prozessentwécklung: Gratis Testversioune mat Optimiséierung.

Global Training: Alljährlech technesch Workshops iwwer Ënnerhalt a Fehlerbehebung.

3. Veraarbechtung vu verschiddene Materialien

SiC: Waferverdënnung op 100 μm mat Ra <0,1 nm.

Saphir: 50 μm Déckt fir UV-Laserfënsteren (Transmittanz >92%@200 nm).

4. Wäertvoll Servicer

Verbrauchsmaterial: Diamantscheiwen (2000+ Waferen/Liewensdauer) a CMP-Schläim.

Conclusioun

Dës Ausrüstung fir d'Verdënnung vu Wafers bitt branchenféierend Präzisioun, Villfältegkeet u verschiddene Materialien an intelligent Automatiséierung, wat se onverzichtbar fir 3D-Integratioun an Energieelektronik mécht. Déi ëmfaassend Servicer vun XKH - vun der Personnaliséierung bis zur Nowveraarbechtung - suergen dofir, datt d'Clienten Käschteeffizienz an exzellent Leeschtung an der Hallefleederproduktioun erreechen.