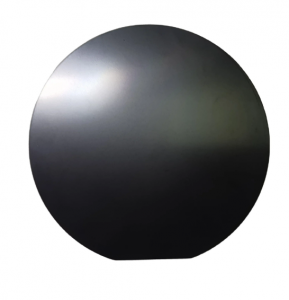

SOI-Waferisolator op Silizium 8-Zoll an 6-Zoll SOI (Silicon-On-Insulator) Waferen

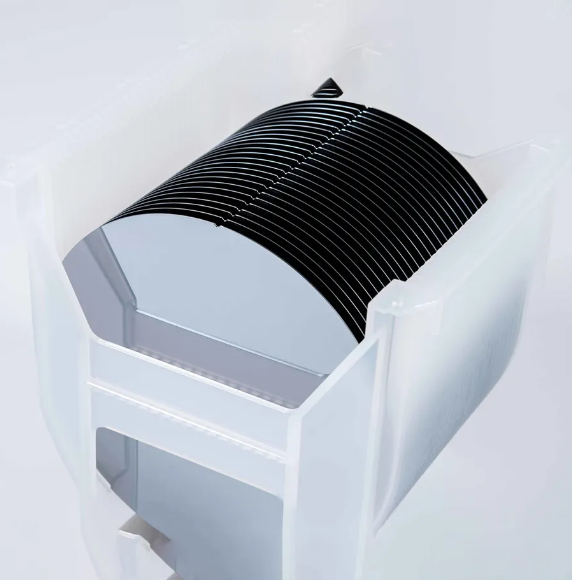

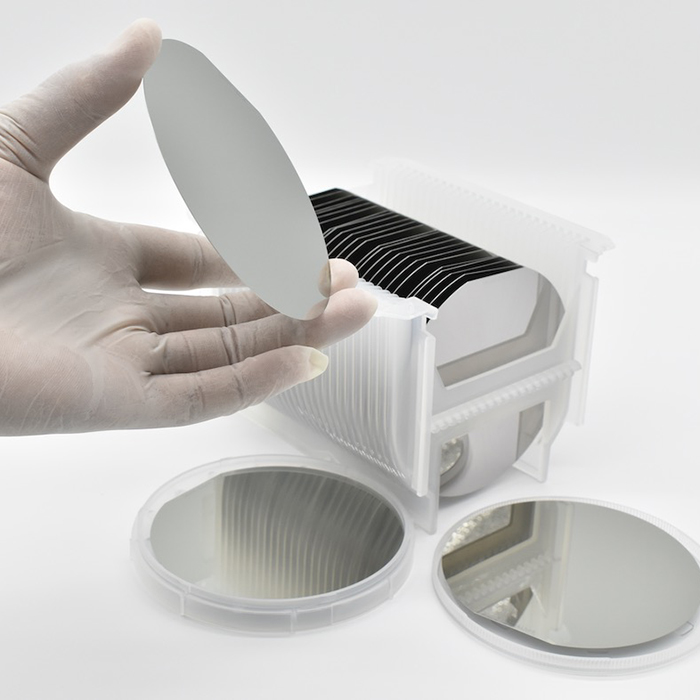

Aféierung vun der Waferbox

Aus enger ieweschter Siliziumschicht, enger isoléierender Oxidschicht an engem ënneschte Siliziumsubstrat bitt den dräischichtege SOI-Wafer ongehéiert Virdeeler an der Mikroelektronik an den HF-Beräicher. Déi iewescht Siliziumschicht, mat héichwäertegem kristallinem Silizium, erliichtert d'Integratioun vu komplexen elektronesche Komponenten mat Präzisioun an Effizienz. Déi isoléierend Oxidschicht, déi virsiichteg entwéckelt gouf fir parasitär Kapazitéit ze minimiséieren, verbessert d'Leeschtung vum Apparat andeems se ongewollt elektresch Stéierungen reduzéiert. Dat ënnescht Siliziumsubstrat bitt mechanesch Ënnerstëtzung a garantéiert Kompatibilitéit mat existente Siliziumveraarbechtungstechnologien.

An der Mikroelektronik déngt de SOI-Wafer als Basis fir d'Fabrikatioun vun fortgeschrattenen integréierte Schaltungen (ICs) mat iwwerleeëner Geschwindegkeet, Energieeffizienz a Zouverlässegkeet. Seng dräischichteg Architektur erméiglecht d'Entwécklung vu komplexe Hallefleiterkomponenten wéi CMOS (Complementary Metal-Oxide-Semiconductor) ICs, MEMS (Micro-Electro-Mechanical Systems) a Kraaftelementer.

Am RF-Beräich weist de SOI-Wafer eng bemierkenswäert Leeschtung beim Design an der Ëmsetzung vun RF-Geräter a Systemer. Seng niddreg parasitär Kapazitéit, héich Duerchbrochspannung an exzellent Isolatiounseigenschaften maachen en zu engem idealen Substrat fir RF-Schalter, Verstärker, Filter an aner RF-Komponenten. Zousätzlech mécht déi inherent Stralungstoleranz vum SOI-Wafer en gëeegent fir Loftfaart- a Verteidegungsapplikatiounen, wou Zouverlässegkeet an haarden Ëmfeld vun essentieller Bedeitung ass.

Ausserdeem erstreckt sech d'Villsäitegkeet vum SOI-Wafer op nei Technologien wéi photonesch integréiert Schaltungen (PICs), wou d'Integratioun vun opteschen an elektronesche Komponenten op engem eenzege Substrat villverspriechend fir Telekommunikatiouns- a Datenkommunikatiounssystemer vun der nächster Generatioun ass.

Zesummegefaasst steet den dräischichtege Silicon-On-Insulator (SOI) Wafer un der Spëtzt vun der Innovatioun an der Mikroelektronik an HF-Applikatiounen. Seng eenzegaarteg Architektur an aussergewéinlech Leeschtungseigenschaften maachen de Wee fräi fir Fortschrëtter an ënnerschiddlechen Industrien, dreiwen de Fortschrëtt un a gestalten d'Zukunft vun der Technologie.

Detailéiert Diagramm