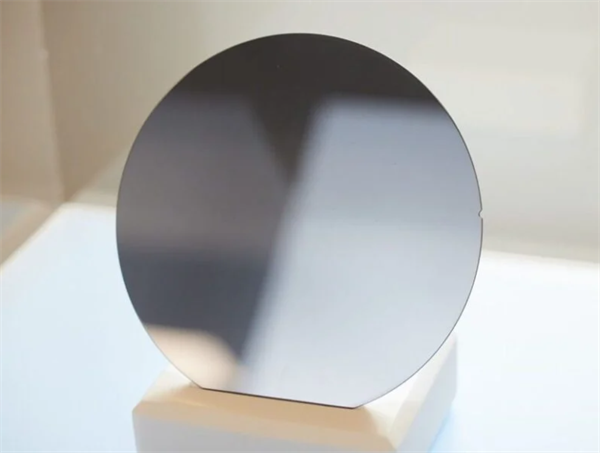

P-Typ SiC Wafer 4H/6H-P 3C-N 6 Zoll Déckt 350 μm mat primärer flaacher Orientéierung

Spezifikatioun 4H/6H-P Typ SiC Kompositsubstrater Gemeinsam Parametertabell

6 Siliziumkarbid (SiC)-Substrat mat engem Duerchmiesser vun Zoll Spezifikatioun

| Grad | Null MPD ProduktiounKlass (Z Grad) | StandardproduktiounGrad (P Grad) | Dummy-Klass (D Grad) | ||

| Duerchmiesser | 145,5 mm~150,0 mm | ||||

| Déckt | 350 μm ± 25 μm | ||||

| Wafer Orientéierung | -OffAchs: 2,0°-4,0° Richtung [1120] ± 0,5° fir 4H/6H-P, Op der Achs: 〈111〉± 0,5° fir 3C-N | ||||

| Mikropäifdicht | 0 cm-2 | ||||

| Widderstandsfäegkeet | p-Typ 4H/6H-P | ≤0,1 Ωꞏcm | ≤0,3 Ωꞏcm | ||

| n-Typ 3C-N | ≤0,8 mΩꞏcm | ≤1 m Ωꞏcm | |||

| Primär flaach Orientéierung | 4H/6H-P | -{1010} ± 5,0° | |||

| 3C-N | -{110} ± 5,0° | ||||

| Primär flaach Längt | 32,5 mm ± 2,0 mm | ||||

| Sekundär flaach Längt | 18,0 mm ± 2,0 mm | ||||

| Sekundär flaach Orientéierung | Silikonfläch no uewen: 90° mat der rietser Säit vun der Prime-Flaachfläch ± 5,0° | ||||

| Randausgrenzung | 3 mm | 6 mm | |||

| LTV/TTV/Béi/Verzerrung | ≤2,5 μm/≤5 μm/≤15 μm/≤30 μm | ≤10 μm/≤15 μm/≤25 μm/≤40 μm | |||

| Rauheet | Polnesch Ra≤1 nm | ||||

| CMP Ra≤0,2 nm | Ra≤0,5 nm | ||||

| Kantrëss duerch héichintensivt Liicht | Keen | Kumulativ Längt ≤ 10 mm, eenzel Längt ≤ 2 mm | |||

| Sechseckplacken duerch héichintensivt Liicht | Kumulativ Fläch ≤0,05% | Kumulativ Fläch ≤0,1% | |||

| Polytypberäicher duerch héichintensivt Liicht | Keen | Kumulativ Fläch ≤3% | |||

| Visuell Kuelestoffinklusiounen | Kumulativ Fläch ≤0,05% | Kumulativ Fläch ≤3% | |||

| Siliziumoberfläche kraazt duerch héichintensivt Liicht | Keen | Kumulativ Längt ≤1 × Waferduerchmiesser | |||

| Kantchips mat héijer Intensitéit vum Liicht | Keen erlaabt ≥0,2 mm Breet an Déift | 5 erlaabt, ≤1 mm all | |||

| Siliziumoberflächenkontaminatioun duerch héich Intensitéit | Keen | ||||

| Verpackung | Multi-Wafer-Kassett oder Eenzelwafer-Behälter | ||||

Notizen:

※ Defektlimite gëllen fir déi ganz Waferuewerfläch ausser dem Randausschlussberäich. # D'Kratzer solle op der Si-Uewerfläch iwwerpréift ginn

De P-Typ SiC Wafer, 4H/6H-P 3C-N, spillt mat senger Gréisst vun 6 Zoll an 350 μm Déckt eng entscheedend Roll an der industrieller Produktioun vun héichperformanter Leeschtungselektronik. Seng exzellent Wärmeleitfäegkeet a seng héich Duerchschlagspannung maachen en ideal fir d'Produktioun vu Komponenten wéi Stroumschalter, Dioden an Transistoren, déi an Héichtemperaturëmfeld wéi Elektroautoen, Stroumnetzer an erneierbaren Energiesystemer agesat ginn. D'Fäegkeet vum Wafer, effizient ënner haarde Bedéngungen ze funktionéieren, garantéiert eng zouverlässeg Leeschtung an industriellen Uwendungen, déi eng héich Leeschtungsdicht an Energieeffizienz erfuerderen. Zousätzlech hëlleft seng primär flaach Orientéierung bei der präziser Ausriichtung während der Fabrikatioun vun den Apparater, wat d'Produktiounseffizienz an d'Produktkonsistenz verbessert.

D'Virdeeler vun N-Typ SiC Kompositsubstrater enthalen

- Héich thermesch KonduktivitéitP-Typ SiC-Wafers verdeelen d'Hëtzt effizient, wouduerch se ideal fir Héichtemperaturapplikatioune sinn.

- Héich DuerchbrochspannungFäeg fir héich Spannungen ze widderstoen, wat Zouverlässegkeet an der Leeschtungselektronik an Héichspannungsapparater garantéiert.

- Resistenz géint haart ËmfeldExcellent Haltbarkeet ënner extremen Bedingungen, wéi héijen Temperaturen a korrosiven Ëmfeld.

- Effizient EnergiekonversiounD'P-Typ Dotierung erliichtert eng effizient Energieveraarbechtung, wouduerch de Wafer fir Energiekonversiounssystemer gëeegent ass.

- Primär flaach OrientéierungGarantéiert eng präzis Ausriichtung während der Produktioun, verbessert d'Genauegkeet an d'Konsistenz vum Apparat.

- Dënn Struktur (350 μm)Déi optimal Déckt vum Wafer ënnerstëtzt d'Integratioun an fortgeschratt, platzbegrenzt elektronesch Apparater.

Insgesamt bitt de P-Typ SiC Wafer, 4H/6H-P 3C-N, eng Rei vu Virdeeler, déi en héich gëeegent fir industriell an elektronesch Uwendungen maachen. Seng héich Wärmeleitfäegkeet a Duerchbrochspannung erméiglechen e verlässleche Betrib an Héichtemperatur- an Héichspannungsëmfeld, während seng Resistenz géint haart Konditiounen Haltbarkeet garantéiert. D'P-Typ Dotierung erlaabt eng effizient Energiekonversioun, wat en ideal fir Leeschtungselektronik an Energiesystemer mécht. Zousätzlech garantéiert déi primär flaach Orientéierung vum Wafer eng präzis Ausriichtung während dem Fabrikatiounsprozess, wat d'Produktiounskonsistenz verbessert. Mat enger Déckt vun 350 μm ass e gutt geegent fir d'Integratioun an fortgeschratt, kompakt Apparater.

Detailéiert Diagramm