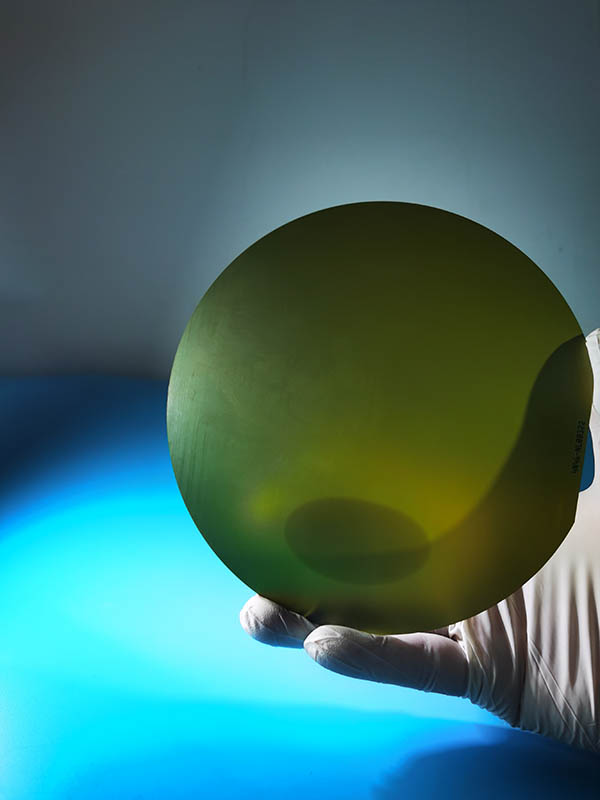

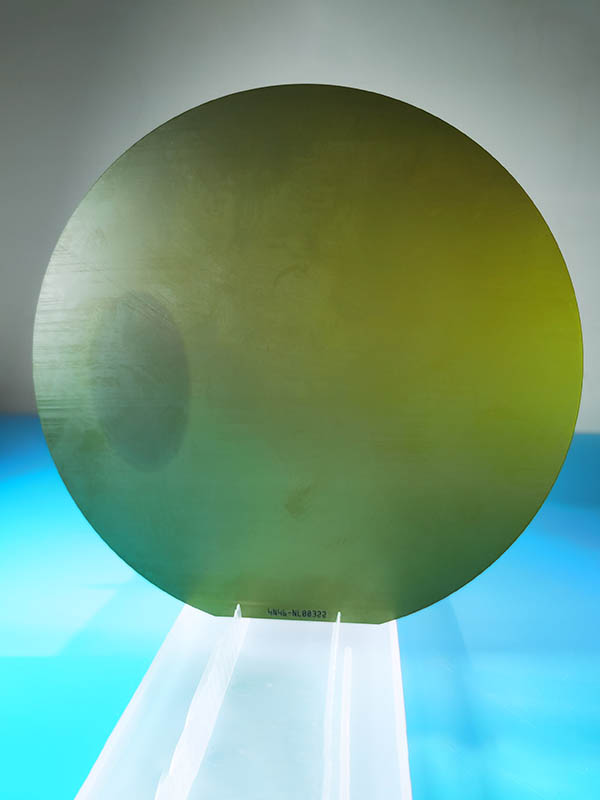

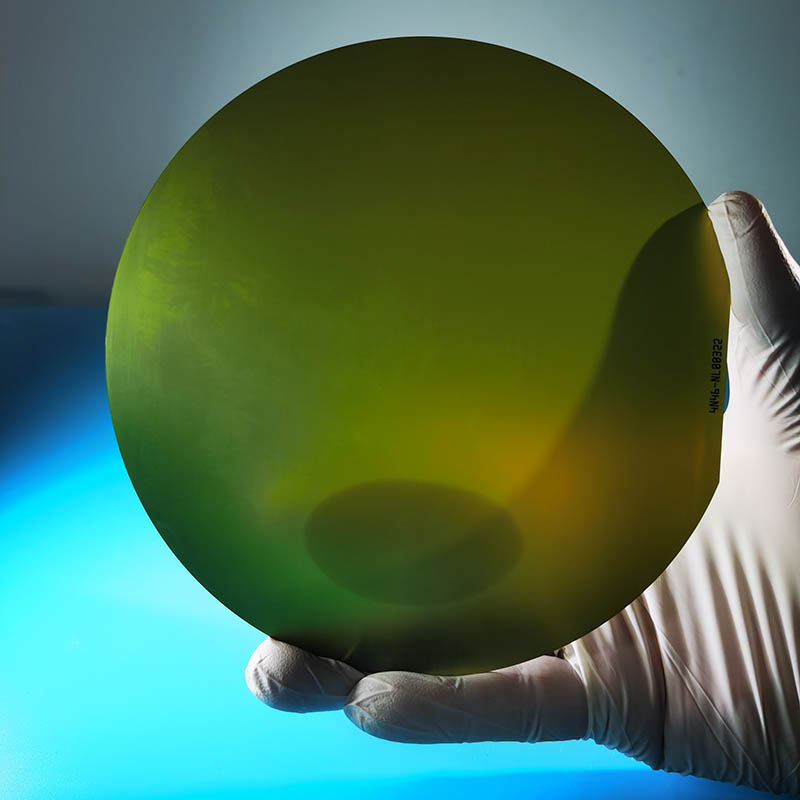

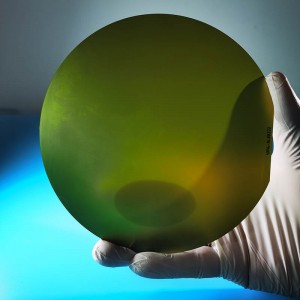

8 Zoll 200 mm 4H-N SiC Wafer leetfäeg Dummy Fuerschungsqualitéit

Wéinst senge eenzegaartege physikaleschen an elektroneschen Eegeschafte gëtt 200 mm SiC Wafer Hallefleedermaterial benotzt fir héich performant, héichtemperaturbeständeg, strahlungsbeständeg an héichfrequent elektronesch Geräter ze kreéieren. De Präis vun 8 Zoll SiC Substrater fällt lues a lues, well d'Technologie méi fortgeschratt gëtt an d'Nofro wiisst. Rezent technologesch Entwécklungen féieren zu enger Produktiounsgréisst vun 200 mm SiC Waferen. Déi Haaptvirdeeler vu SiC Wafer Hallefleedermaterialien am Verglach mat Si- a GaAs-Waferen: D'elektresch Feldstäerkt vu 4H-SiC beim Lawinenduerchbroch ass méi wéi eng Gréisstenuerdnung méi héich wéi déi entspriechend Wäerter fir Si a GaAs. Dëst féiert zu enger bedeitender Ofsenkung vum On-State-Widerstand Ron. En niddrege On-State-Widerstand, kombinéiert mat héijer Stroumdicht an thermescher Konduktivitéit, erlaabt d'Benotzung vu ganz klenge Chips fir Stroumgeräter. Déi héich thermesch Konduktivitéit vu SiC reduzéiert den thermesche Widderstand vum Chip. Déi elektronesch Eegeschafte vun Apparater op Basis vu SiC Waferen si ganz stabil mat der Zäit an bei der Temperatur, wat eng héich Zouverlässegkeet vun de Produkter garantéiert. Siliziumcarbid ass extrem resistent géint haart Stralung, wat d'elektronesch Eegeschafte vum Chip net verschlechtert. Déi héich limitéiert Betribstemperatur vum Kristall (méi wéi 6000°C) erlaabt Iech, héich zouverlässeg Apparater fir haart Betribsbedingungen a speziell Uwendungen ze kreéieren. Am Moment kënne mir kleng Chargen vun 200 mmSiC-Waferen stänneg a kontinuéierlech liwweren an hunn e puer Lagerbestänn.

Spezifikatioun

| Zuel | Artikel | Eenheet | Produktioun | Fuerschung | Dummy |

| 1. Parameteren | |||||

| 1.1 | Polytyp | -- | 4H | 4H | 4H |

| 1.2 | Uewerflächenorientéierung | ° | <11-20>4±0.5 | <11-20>4±0.5 | <11-20>4±0.5 |

| 2. Elektresch Parameter | |||||

| 2.1 | Dotiermëttel | -- | n-Typ Stéckstoff | n-Typ Stéckstoff | n-Typ Stéckstoff |

| 2.2 | Widderstand | ohm ·cm | 0,015~0,025 | 0,01~0,03 | NA |

| 3. Mechanesch Parameter | |||||

| 3.1 | Duerchmiesser | mm | 200±0,2 | 200±0,2 | 200±0,2 |

| 3.2 | Déckt | μm | 500±25 | 500±25 | 500±25 |

| 3.3 | Notch Orientéierung | ° | [1-100]±5 | [1-100]±5 | [1-100]±5 |

| 3.4 | Kerbdéift | mm | 1~1,5 | 1~1,5 | 1~1,5 |

| 3.5 | LTV | μm | ≤5 (10mm * 10mm) | ≤5 (10mm * 10mm) | ≤10 (10mm * 10mm) |

| 3.6 | TTV | μm | ≤10 | ≤10 | ≤15 |

| 3.7 | Béi | μm | -25~25 | -45~45 | -65~65 |

| 3.8 | Ketten | μm | ≤30 | ≤50 | ≤70 |

| 3.9 | AFM | nm | Ra≤0,2 | Ra≤0,2 | Ra≤0,2 |

| 4. Struktur | |||||

| 4.1 | Mikropäifdicht | ea/cm² | ≤2 | ≤10 | ≤50 |

| 4.2 | Metallgehalt | Atomer/cm² | ≤1E11 | ≤1E11 | NA |

| 4.3 | TSD | ea/cm² | ≤500 | ≤1000 | NA |

| 4.4 | BPD | ea/cm² | ≤2000 | ≤5000 | NA |

| 4.5 | TED | ea/cm² | ≤7000 | ≤10000 | NA |

| 5. Positiv Qualitéit | |||||

| 5.1 | vir | -- | Si | Si | Si |

| 5.2 | Uewerflächenfinish | -- | Si-Face CMP | Si-Face CMP | Si-Face CMP |

| 5.3 | Partikel | ea/Waffel | ≤100 (Gréisst ≥0,3μm) | NA | NA |

| 5.4 | krazen | ea/Waffel | ≤5, Gesamtlängt ≤200mm | NA | NA |

| 5.5 | Rand Abschnitzen/Verdéiwungen/Rëss/Flecken/Kontaminatioun | -- | Keen | Keen | NA |

| 5.6 | Polytyp-Gebidder | -- | Keen | Fläch ≤10% | Fläch ≤30% |

| 5.7 | Frontmarkéierung | -- | Keen | Keen | Keen |

| 6. Réckqualitéit | |||||

| 6.1 | Réckfinish | -- | C-Face MP | C-Face MP | C-Face MP |

| 6.2 | krazen | mm | NA | NA | NA |

| 6.3 | Réckdefekter um Rand Stécker/Verdéiwungen | -- | Keen | Keen | NA |

| 6.4 | Réckrauheet | nm | Ra≤5 | Ra≤5 | Ra≤5 |

| 6.5 | Réckmarkéierung | -- | Kerb | Kerb | Kerb |

| 7. Rand | |||||

| 7.1 | Rand | -- | Fassung | Fassung | Fassung |

| 8. Pak | |||||

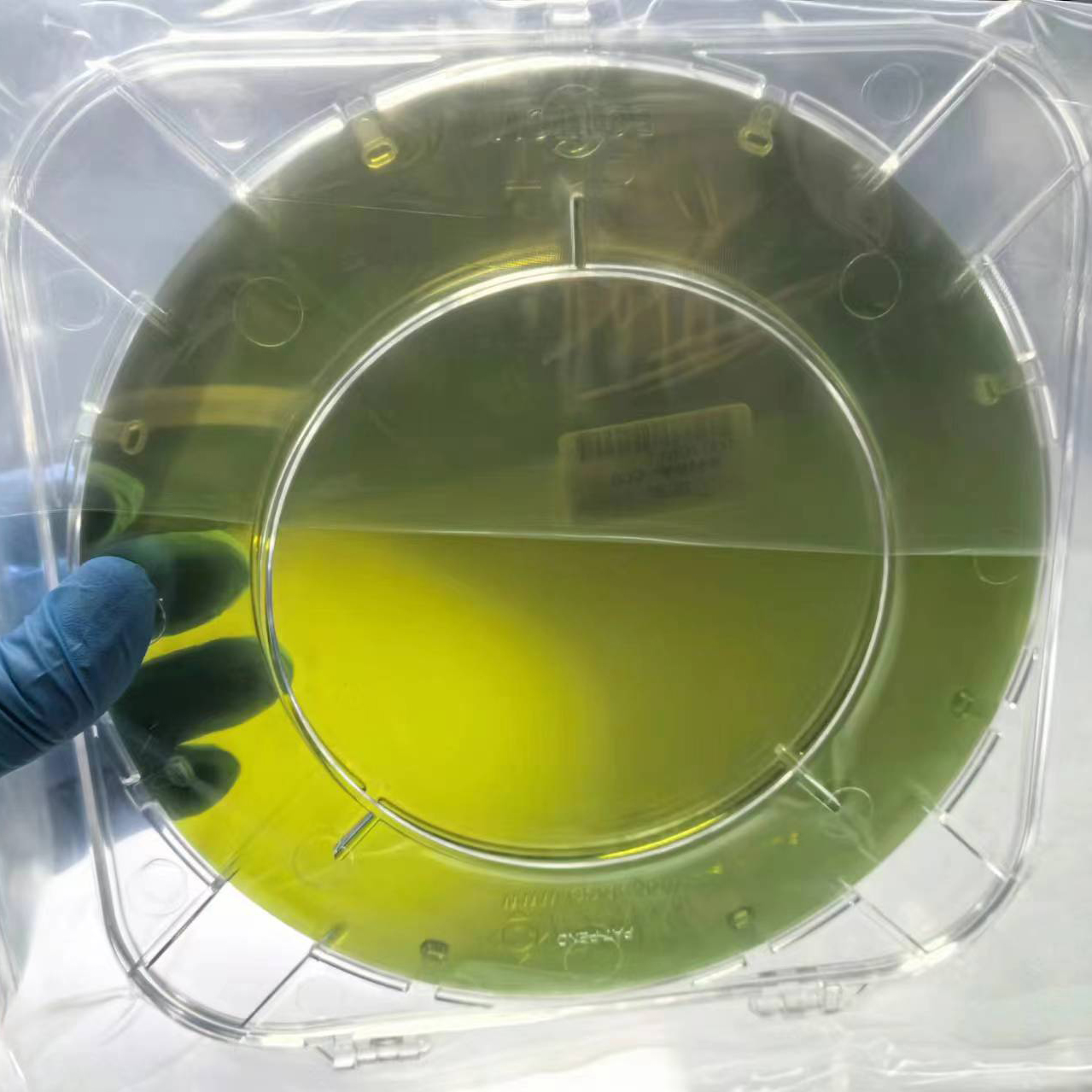

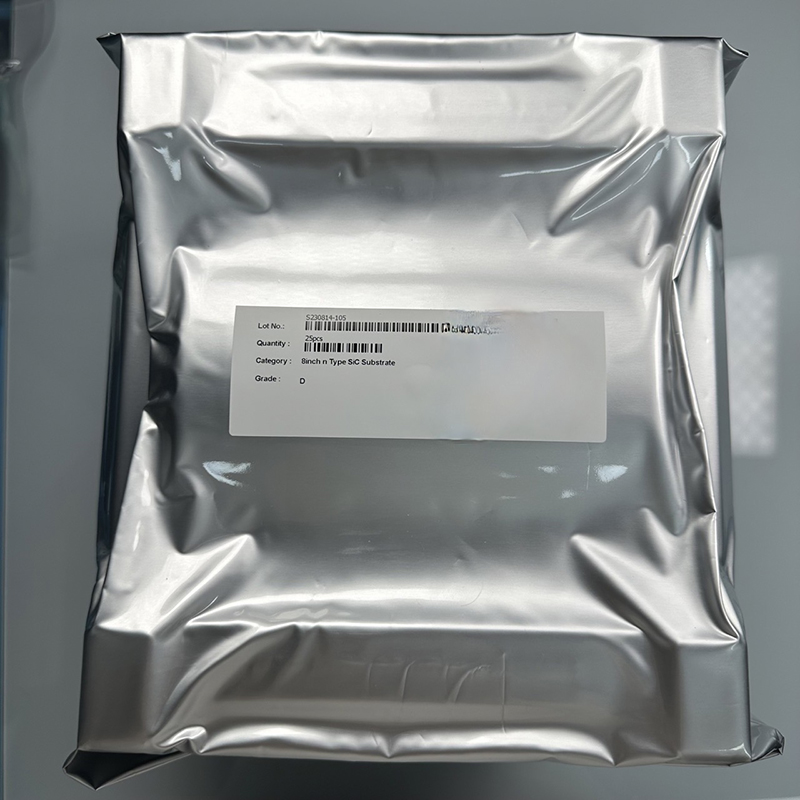

| 8.1 | Verpackung | -- | Epi-ready mat Vakuum Verpackung | Epi-ready mat Vakuum Verpackung | Epi-ready mat Vakuum Verpackung |

| 8.2 | Verpackung | -- | Multi-Wafer Kassettenverpackung | Multi-Wafer Kassettenverpackung | Multi-Wafer Kassettenverpackung |

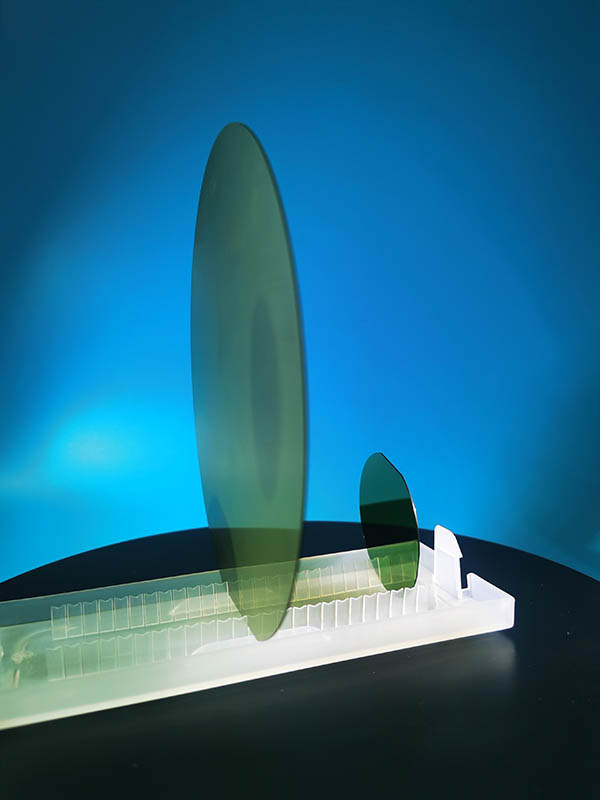

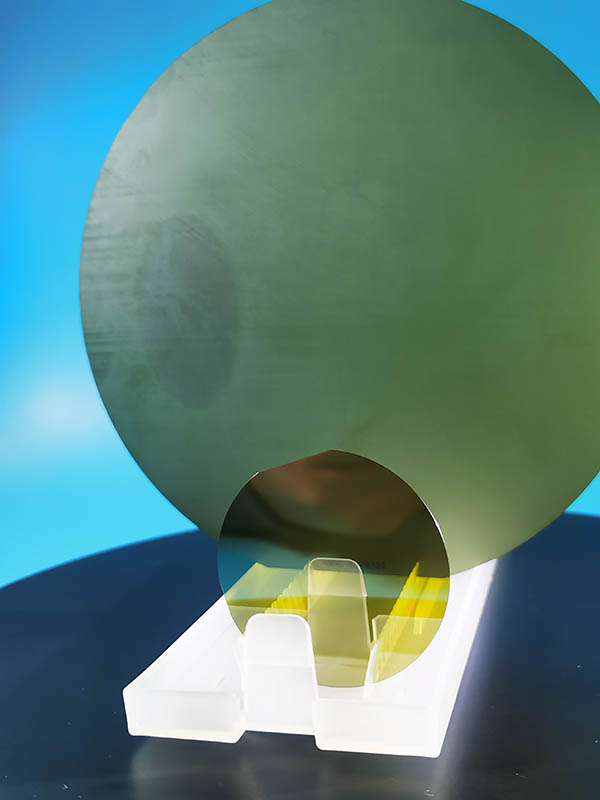

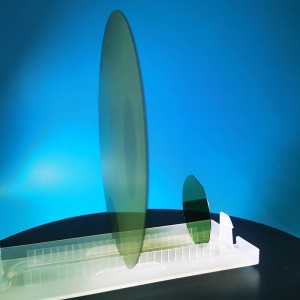

Detailéiert Diagramm