4 Zoll SiC Wafers 6H Hallefisoléierend SiC Substrater Prime-, Fuerschungs- a Dummy-Qualitéit

Produktspezifikatioun

| Grad | Null MPD Produktiounsgrad (Z-Grad) | Standard Produktiounsgrad (P-Grad) | Dummy-Klass (Klass D) | ||||||||

| Duerchmiesser | 99,5 mm~100,0 mm | ||||||||||

| 4H-SI | 500 μm ± 20 μm | 500 μm ± 25 μm | |||||||||

| Wafer Orientéierung |

Off-Achs: 4,0° Richtung < 1120 > ±0,5° fir 4H-N, Op-Achs: < 0001 > ±0,5° fir 4H-SI | ||||||||||

| 4H-SI | ≤1cm-2 | ≤5 cm-2 | ≤15 cm-2 | ||||||||

| 4H-SI | ≥1E9 Ω·cm | ≥1E5 Ω·cm | |||||||||

| Primär flaach Orientéierung | {10-10} ±5,0° | ||||||||||

| Primär flaach Längt | 32,5 mm±2,0 mm | ||||||||||

| Sekundär flaach Längt | 18,0 mm±2,0 mm | ||||||||||

| Sekundär flaach Orientéierung | Silikon-Uewerfläch no uewen: 90° mat der rietser Säit vun der Prime-Flaach ±5,0° | ||||||||||

| Randausgrenzung | 3 mm | ||||||||||

| LTV/TTV/Béi/Verzerrung | ≤3 μm/≤5 μm/≤15 μm/≤30 μm | ≤10 μm/≤15 μm/≤25 μm/≤40 μm | |||||||||

| Rauheet | C-Gesiicht | Polnesch | Ra≤1 nm | ||||||||

| Si Gesiicht | CMP | Ra≤0,2 nm | Ra≤0,5 nm | ||||||||

| Kantrëss duerch héichintensivt Liicht | Keen | Kumulativ Längt ≤ 10 mm, eenzel Längt ≤2 mm | |||||||||

| Sechseckplacken duerch héichintensivt Liicht | Kumulativ Fläch ≤0,05% | Kumulativ Fläch ≤0,1% | |||||||||

| Polytypberäicher duerch héichintensivt Liicht | Keen | Kumulativ Fläch ≤3% | |||||||||

| Visuell Kuelestoffinklusiounen | Kumulativ Fläch ≤0,05% | Kumulativ Fläch ≤3% | |||||||||

| Siliziumoberfläche kraazt duerch héichintensivt Liicht | Keen | Kumulativ Längt ≤1*Waferduerchmiesser | |||||||||

| Kantchips mat héijer Intensitéit vum Liicht | Keen erlaabt ≥0,2 mm Breet an Déift | 5 erlaabt, ≤1 mm all | |||||||||

| Siliziumoberflächenkontaminatioun duerch héich Intensitéit | Keen | ||||||||||

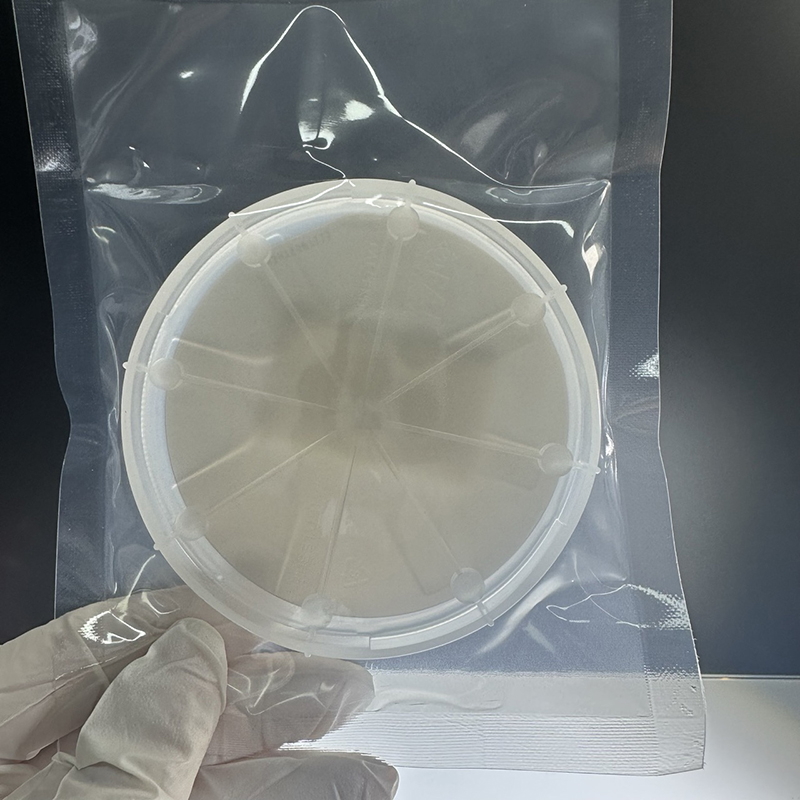

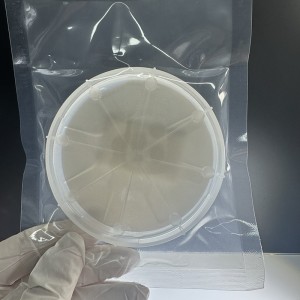

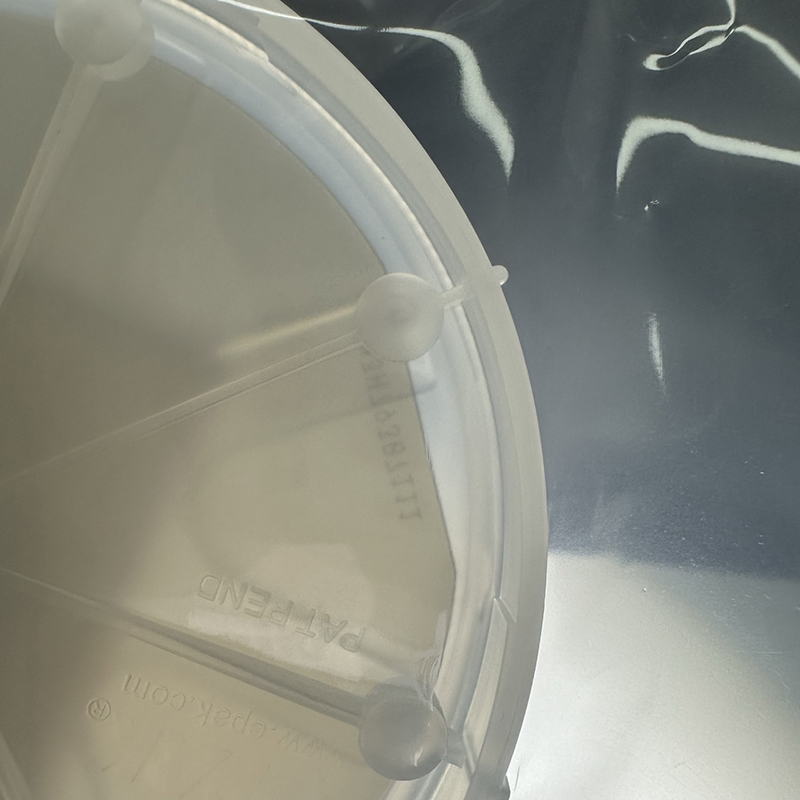

| Verpackung | Multi-Wafer Kassett oder Eenzelwafer Behälter | ||||||||||

Detailéiert Diagramm

Verwandte Produkter

Schreift Är Noriicht hei a schéckt se eis