Inhaltsverzeechnes

1. Technologesche Wandel: Den Opstig vu Siliziumkarbid a seng Erausfuerderungen

2. TSMC seng strategesch Ännerung: GaN verloossen a op SiC setzen

3. Materialkonkurrenz: D'Onverzettlechkeet vu SiC

4. Applikatiounsszenarien: D'Revolutioun vum Thermomanagement an KI-Chips an Elektronik vun der nächster Generatioun

5. Zukünfteg Erausfuerderungen: Technesch Engpässe a Konkurrenz an der Industrie

Laut TechNews ass déi global Hallefleederindustrie an eng Ära agaangen, déi vun der kënschtlecher Intelligenz (KI) an dem High-Performance Computing (HPC) gedriwwe gëtt, wou d'Thermomanagement als e Kär-Engpässe erausgestallt ass, deen Auswierkungen op Chipdesign a Prozessduerchbréch huet. Well fortgeschratt Verpackungsarchitekturen wéi 3D-Stacking an 2,5D-Integratioun weider d'Chipdicht an de Stroumverbrauch erhéijen, kënnen traditionell Keramiksubstrater net méi den Ufuerderunge vum Thermofluss erfëllen. TSMC, déi weltgréisst Wafer-Gießerei, reagéiert op dës Erausfuerderung mat engem däitleche Materialwiessel: si adoptéiert vollstänneg 12-Zoll-Eenkristall-Siliciumcarbid (SiC)-Substrater, während se lues a lues aus dem Galliumnitrid (GaN)-Geschäft erausgeet. Dëse Schrëtt bedeit net nëmmen eng Neikalibrierung vun der Materialstrategie vun TSMC, mä weist och drop hin, wéi d'Thermomanagement vun enger "ënnerstëtzender Technologie" zu engem "Kär-Kompetitive Virdeel" iwwergaangen ass.

Siliziumkarbid: Iwwer d'Leeschtungselektronik eraus

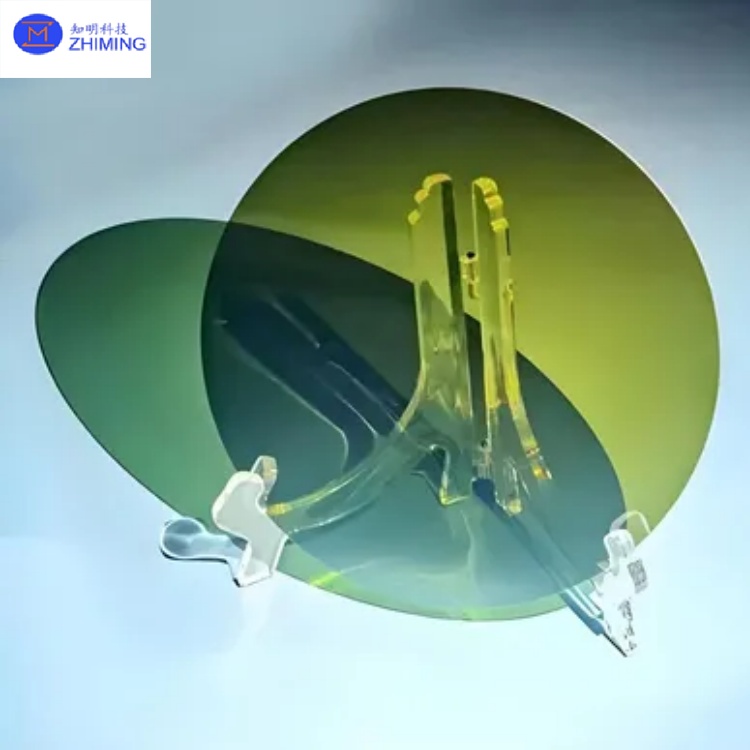

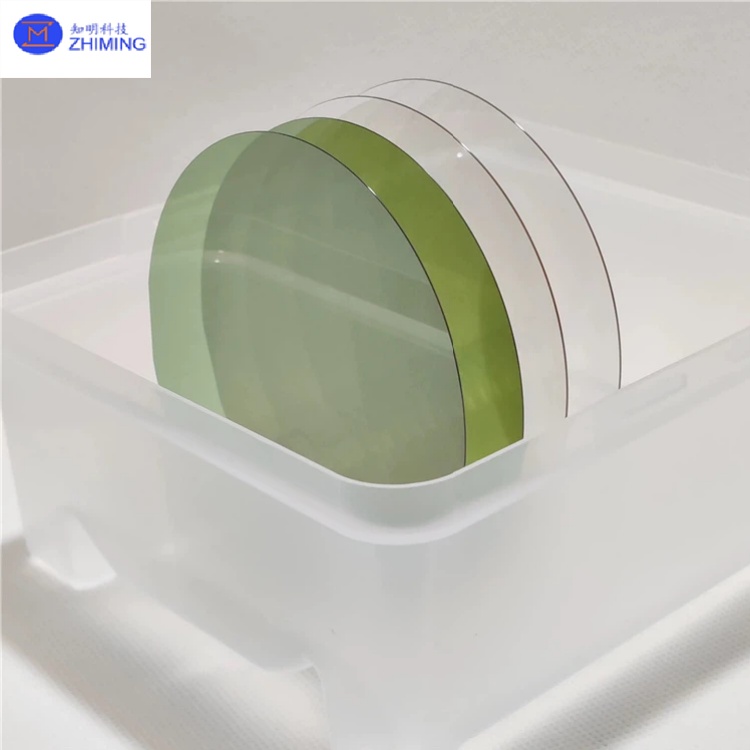

Siliziumkarbid, bekannt fir seng Halbleitereegeschafte mat enger breeder Bandlück, gëtt traditionell an héicheffizienter Leeschtungselektronik wéi Elektroauto-Inverter, industriell Motorsteierungen an erneierbarer Energieinfrastruktur benotzt. De Potenzial vu SiC geet awer wäit driwwer eraus. Mat enger aussergewéinlecher Wärmeleitfäegkeet vu ronn 500 W/mK - déi wäit iwwer konventionell Keramiksubstrater wéi Aluminiumoxid (Al₂O₃) oder Saphir läit - ass SiC elo bereet, déi ëmmer méi thermesch Erausfuerderunge vun Uwendungen mat héijer Dicht ze bewältegen.

KI-Beschleuniger an d'Thermesch Kris

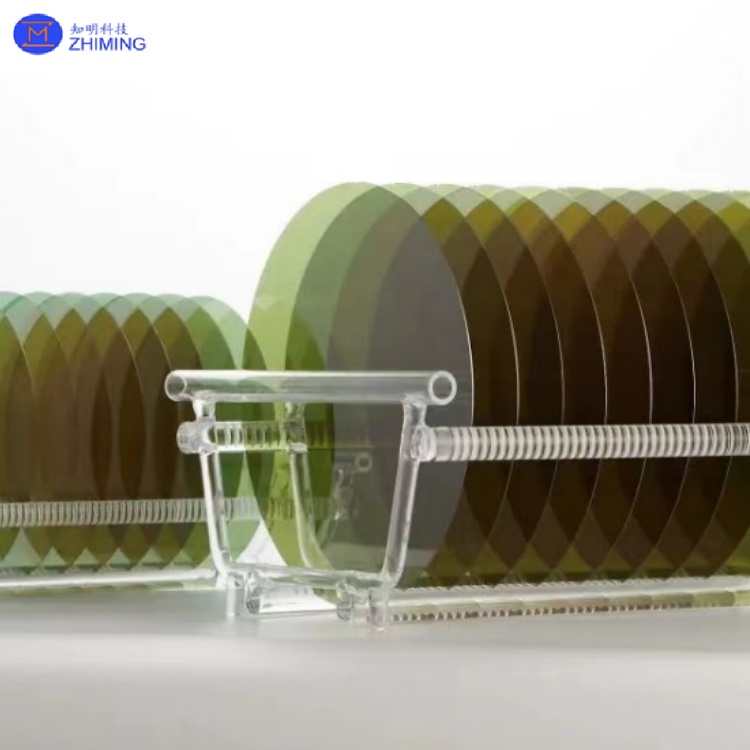

D'Verbreedung vun KI-Beschleuniger, Datacenter-Prozessoren an AR-Smartglasse huet d'räumlech Aschränkungen an d'Thermomanagement-Dilemmaer verschäerft. Bei tragbare Geräter, zum Beispill, erfuerderen Mikrochipkomponenten, déi no beim A positionéiert sinn, eng präzis Thermokontroll, fir Sécherheet a Stabilitéit ze garantéieren. TSMC notzt seng Joerzéngte laang Expertise an der Fabrikatioun vun 12-Zoll-Wafers a fërdert groussflächeg Eenzelkristall-SiC-Substrater, fir traditionell Keramik z'ersetzen. Dës Strategie erméiglecht eng nahtlos Integratioun an existent Produktiounslinnen, wouduerch Rendement a Käschtevirdeeler ausbalancéiert ginn, ouni datt eng komplett Produktiounsrenovéierung néideg ass.

Technesch Erausfuerderungen an Innovatiounenan

anD'Roll vu SiC an der fortgeschrattener Verpackung

- 2.5D Integratioun:Chips sinn op Silizium- oder organeschen Zwëschenschalter mat kuerzen, effiziente Signalweeër montéiert. D'Erausfuerderunge vun der Hëtzofleedung sinn hei haaptsächlech horizontal.

- 3D-Integratioun:Vertikal gestapelte Chips iwwer Through-Silicon Vias (TSVs) oder Hybrid Bonding erreechen eng ultrahéich Verbindungsdicht, awer si stinn ënner exponentiellem thermesche Drock. SiC déngt net nëmmen als passivt thermescht Material, mä synergiséiert och mat fortgeschrattene Léisunge wéi Diamant oder flëssegt Metall fir "Hybrid-Kühlsystemer" ze bilden.

anStrategeschen Ausstieg aus GaN

Iwwer d'Automobilindustrie eraus: Déi nei Grenzen vu SiC

- Konduktiv N-Typ SiC:Funktionéiert als Wärmestreider an KI-Beschleuniger an Héichleistungsprozessoren.

- Isoléierend SiC:Déngt als Interposer a Chiplet-Designen, wou se d'elektresch Isolatioun mat der thermescher Leedung ausbalancéieren.

Dës Innovatiounen positionéieren SiC als Grondmaterial fir d'Wärmemanagement an KI a Chips fir Datenzentren.

Déi materiell Landschaft

D'Expertise vun TSMC am Beräich vun 12-Zoll-Wafers ënnerscheet et vun de Konkurrenten, andeems et eng séier Verdeelung vu SiC-Plattformen erméiglecht. Andeems et déi existent Infrastruktur an fortgeschratt Verpackungstechnologien wéi CoWoS notzt, zielt TSMC drop of, Materialvirdeeler an thermesch Léisungen op Systemniveau ëmzewandelen. Gläichzäiteg leeën Industrierisen wéi Intel Prioritéit op d'Stroumversuergung um Réck an op d'Co-Design vun der thermescher Energieversuergung, wat de globale Wandel a Richtung thermeschzentrierter Innovatioun ënnersträicht.

Zäitpunkt vun der Verëffentlechung: 28. September 2025