Am boomenden Entwécklungsprozess vun der Hallefleederindustrie, poléiert EenkristallSiliziumwaferenspillen eng entscheedend Roll. Si déngen als Grondmaterial fir d'Produktioun vu verschiddene mikroelektroneschen Apparater. Vu komplexen an präzisen integréierte Schaltungen bis hin zu Héichgeschwindegkeetsmikroprozessoren a multifunktionelle Sensoren, poléiert EenkristallSiliziumwaferensinn essentiell. D'Ënnerscheeder an hirer Leeschtung a Spezifikatioune beaflossen direkt d'Qualitéit an d'Leeschtung vun de fäerdege Produkter. Hei sinn déi üblech Spezifikatiounen a Parameter vu poléierte Singlekristall-Siliciumwaferen:

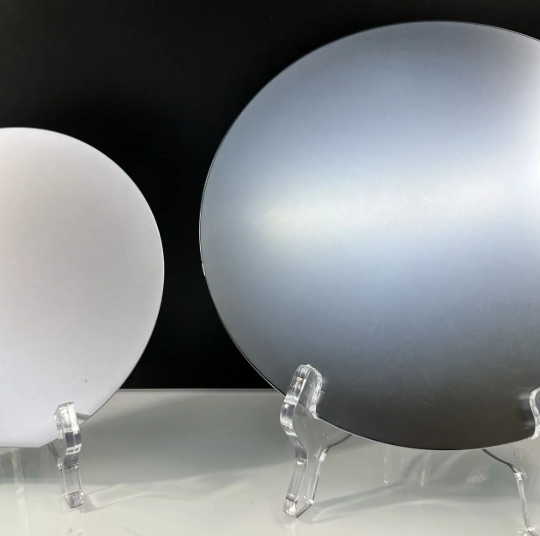

Duerchmiesser: D'Gréisst vun Hallefleiter-Eenkristall-Siliciumwafer gëtt un hirem Duerchmiesser gemooss, an et gëtt se a verschiddene Spezifikatiounen. Déi üblech Duerchmiesser sinn 2 Zoll (50,8 mm), 3 Zoll (76,2 mm), 4 Zoll (100 mm), 5 Zoll (125 mm), 6 Zoll (150 mm), 8 Zoll (200 mm), 12 Zoll (300 mm) an 18 Zoll (450 mm). Verschidde Duerchmiesser si fir verschidde Produktiounsbedürfnisser a Prozessufuerderunge gëeegent. Zum Beispill gi Wafere mat méi klengem Duerchmiesser dacks fir speziell, kleng-volumen Mikroelektronik-Apparater benotzt, während Wafere mat méi groussen Duerchmiesser eng méi héich Produktiounseffizienz a Käschtevirdeeler bei der grousser Integratiounsschaltung weisen. D'Uewerflächenufuerderunge ginn als eenzeg Säit poléiert (SSP) an duebel Säit poléiert (DSP) kategoriséiert. Eenzel Säit poléiert Wafere gi fir Apparater benotzt, déi eng héich Flaachheet op enger Säit erfuerderen, wéi zum Beispill bestëmmte Sensoren. Duebel Säit poléiert Wafere gi meeschtens fir integréiert Schaltungen an aner Produkter benotzt, déi eng héich Präzisioun op béide Flächen erfuerderen. Uewerflächenufuerderungen (Finish): Eensäiteg poléiert SSP / Duebelsäiteg poléiert DSP.

Typ/Dotierstoff: (1) N-Typ Hallefleeder: Wann bestëmmt Onreinheetsatome an den intrinsesche Hallefleeder agefouert ginn, änneren si seng Konduktivitéit. Zum Beispill, wann fënnefwäerteg Elementer wéi Stickstoff (N), Phosphor (P), Arsen (As) oder Antimon (Sb) bäigefüügt ginn, bilden hir Valenzelektrone kovalent Bindungen mat de Valenzelektrone vun den ëmleienden Siliziumatome, wouduerch en zousätzlechen Elektron net duerch eng kovalent Bindung gebonnen ass. Dëst resultéiert an enger Elektronekonzentratioun, déi méi grouss ass wéi d'Lachkonzentratioun, wouduerch en N-Typ Hallefleeder entsteet, och bekannt als Elektronen-Typ Hallefleeder. N-Typ Hallefleeder si wichteg bei der Fabrikatioun vun Apparater, déi Elektrone als Haaptladungsträger brauchen, wéi zum Beispill bestëmmte Stroumversuergungsapparater. (2) P-Typ Hallefleeder: Wann dräiwäerteg Onreinheetselementer wéi Bor (B), Gallium (Ga) oder Indium (In) an den Silizium Hallefleeder agefouert ginn, bilden d'Valenzelektrone vun den Onreinheetsatome kovalent Bindungen mat den ëmleienden Siliziumatome, awer si feelen op d'mannst ee Valenzelektron a kënnen keng komplett kovalent Bindung bilden. Dëst féiert zu enger Lächerkonzentratioun, déi méi grouss ass wéi d'Elektronekonzentratioun, wouduerch e P-Typ Hallefleeder entsteet, och bekannt als Lächer-Typ Hallefleeder. P-Typ Hallefleeder spille eng Schlësselroll bei der Fabrikatioun vun Apparater, bei deenen Lächer als Haaptladungsträger déngen, wéi zum Beispill Dioden a bestëmmten Transistoren.

Widderstand: De Widderstand ass eng Schlësselphysikalesch Gréisst, déi d'elektresch Leetfäegkeet vu poléierte Singlekristall-Siliciumwafer moosst. Säi Wäert reflektéiert d'leetfäegkeetsleeschtung vum Material. Wat méi niddreg de Widderstand, wat besser d'Leetfäegkeet vum Siliziumwafer; am Géigendeel, wat méi héich de Widderstand, wat méi schlecht d'Leetfäegkeet. De Widderstand vu Siliziumwafer gëtt duerch hir inherent Materialeegeschafte bestëmmt, an d'Temperatur huet och e wesentlechen Afloss. Am Allgemengen klëmmt de Widderstand vu Siliziumwafer mat der Temperatur. A prakteschen Uwendungen hunn ënnerschiddlech mikroelektronesch Apparater ënnerschiddlech Widderstandsufuerderunge fir Siliziumwafer. Zum Beispill brauche Waferen, déi an der Fabrikatioun vun integréierte Schaltungen benotzt ginn, eng präzis Kontroll vum Widderstand, fir eng stabil a zouverlässeg Leeschtung vun den Apparater ze garantéieren.

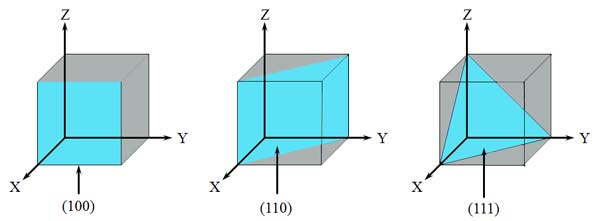

Orientéierung: D'Kristallorientéierung vum Wafer representéiert déi kristallografesch Richtung vum Siliziumgitter, typescherweis spezifizéiert duerch Miller-Indizes wéi (100), (110), (111) etc. Verschidde Kristallorientéierunge hunn ënnerschiddlech physikalesch Eegeschaften, wéi d'Linnendicht, déi jee no Orientéierung variéiert. Dësen Ënnerscheed kann d'Leeschtung vum Wafer an de spéideren Veraarbechtungsschrëtt an d'endgülteg Leeschtung vu mikroelektroneschen Apparater beaflossen. Am Fabrikatiounsprozess kann d'Auswiel vun engem Siliziumwafer mat der passender Orientéierung fir verschidden Apparatufuerderungen d'Apparatleeschtung optimiséieren, d'Produktiounseffizienz verbesseren an d'Produktqualitéit verbesseren.

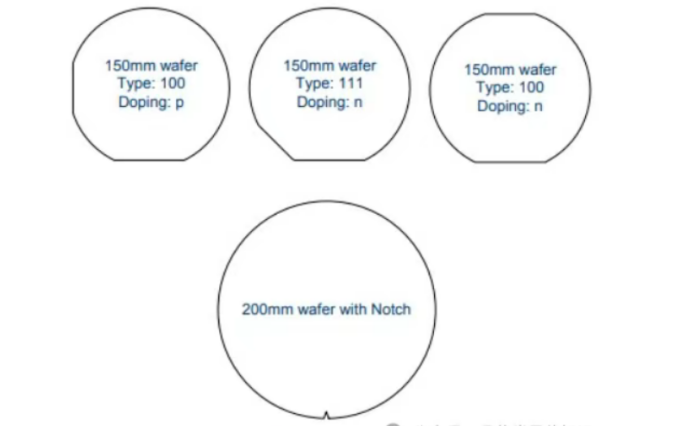

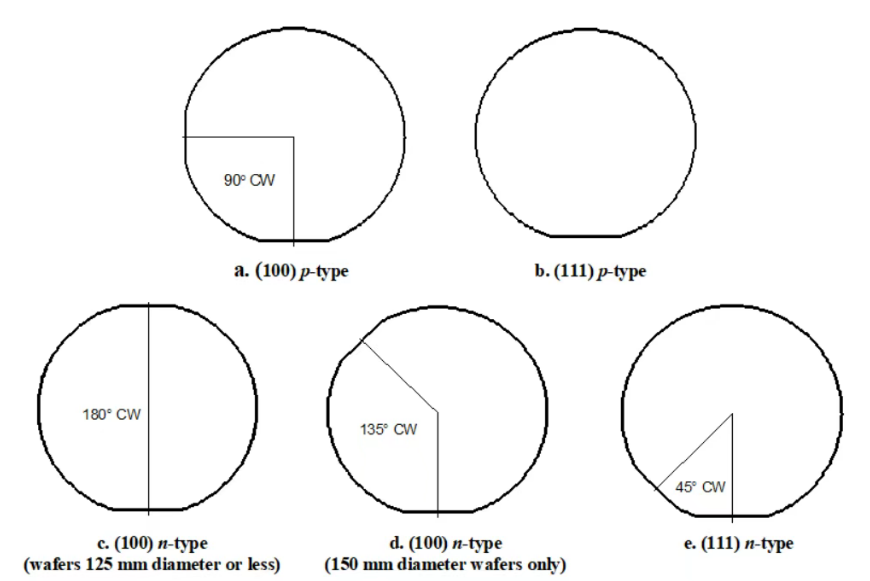

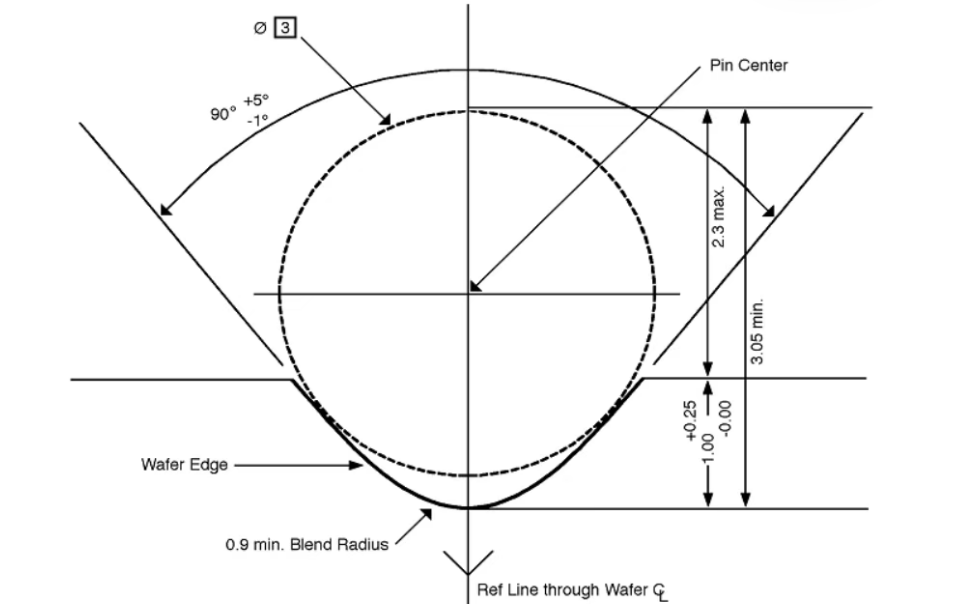

Flaach/Notch: Déi flaach Kant (Flat) oder V-Notch (Notch) um Ëmfang vum Siliziumwafer spillt eng entscheedend Roll bei der Ausriichtung vun der Kristallorientéierung an ass e wichtegen Identifikator bei der Fabrikatioun a Veraarbechtung vum Wafer. Wafere mat verschiddenen Duerchmiesser entspriechen ënnerschiddleche Standarden fir d'Längt vum Flaachen oder Notch. D'Ausriichtungskante ginn a primär Flaach a sekundär Flaach klasséiert. Déi primär Flaach gëtt haaptsächlech benotzt fir d'Basis Kristallorientéierung an d'Veraarbechtungsreferenz vum Wafer ze bestëmmen, während déi sekundär Flaach weider bei der präziser Ausriichtung a Veraarbechtung hëlleft, wat e präzise Betrib a Konsistenz vum Wafer während der ganzer Produktiounslinn garantéiert.

Déckt: D'Déckt vun engem Wafer gëtt typescherweis a Mikrometer (μm) uginn, mat enger üblecher Déckt tëscht 100μm an 1000μm. Wafere mat verschiddenen Déckten si fir verschidden Aarte vu mikroelektroneschen Apparater gëeegent. Méi dënn Wafere (z.B. 100μm - 300μm) ginn dacks fir Chipfabrikatioun benotzt, déi eng strikt Décktkontroll erfuerdert, d'Gréisst a Gewiicht vum Chip reduzéiert an d'Integratiounsdicht erhéicht. Méi déck Wafere (z.B. 500μm - 1000μm) ginn wäit verbreet an Apparater benotzt, déi eng méi héich mechanesch Stäerkt erfuerderen, wéi z.B. Kraafthallefleederapparater, fir d'Stabilitéit während dem Betrib ze garantéieren.

Uewerflächenrauheet: D'Uewerflächenrauheet ass ee vun de Schlësselparameter fir d'Evaluatioun vun der Waferqualitéit, well se direkt d'Adhäsioun tëscht dem Wafer an den spéider ofgesaten Dënnschichtmaterialien, souwéi d'elektresch Leeschtung vum Apparat beaflosst. Si gëtt normalerweis als Root Mean Square (RMS) Rauheet (an nm) ausgedréckt. Eng méi niddreg Uewerflächenrauheet bedeit datt d'Waferuewerfläch méi glat ass, wat hëlleft Phänomener wéi Elektronestreuung ze reduzéieren an d'Leeschtung an d'Zouverlässegkeet vum Apparat ze verbesseren. A fortgeschrattene Hallefleederherstellungsprozesser ginn d'Ufuerderunge fir d'Uewerflächenrauheet ëmmer méi streng, besonnesch fir d'High-End-Herstellung vun integréierte Schaltungen, wou d'Uewerflächenrauheet op e puer Nanometer oder souguer méi niddreg kontrolléiert muss ginn.

Total Décktvariatioun (TTV): Déi total Décktvariatioun bezitt sech op den Ënnerscheed tëscht der maximaler an der minimaler Déckt, déi op verschiddene Punkten op der Waferuewerfläch gemooss gëtt, typescherweis a μm ausgedréckt. En héijen TTV kann zu Ofwäichungen a Prozesser wéi Photolithographie an Ätzung féieren, wat d'Konsistenz an d'Ausbezuelung vun den Apparater beaflosst. Dofir ass d'Kontroll vum TTV während der Waferherstellung e Schlësselschrëtt fir d'Produktqualitéit ze garantéieren. Fir d'Hierstellung vu mikroelektroneschen Apparater mat héijer Präzisioun muss den TTV typescherweis bannent e puer Mikrometer leien.

Béi: Béi bezitt sech op d'Ofwäichung tëscht der Waferuewerfläch an der idealer flaacher Fläch, typescherweis a μm gemooss. Wafere mat exzessiver Béiung kënne bei der spéiderer Veraarbechtung briechen oder ongläichméisseg Belaaschtung erleiden, wat d'Produktiounseffizienz an d'Produktqualitéit beaflosst. Besonnesch a Prozesser, déi eng héich Flächegkeet erfuerderen, wéi z. B. Photolithographie, muss d'Béiung bannent engem spezifesche Beräich kontrolléiert ginn, fir d'Genauegkeet an d'Konsistenz vum photolithographesche Muster ze garantéieren.

Verzerrung: Verzerrung weist d'Ofwäichung tëscht der Waferuewerfläch an der idealer sphärescher Form un, och a μm gemooss. Ähnlech wéi d'Béiung ass Verzerrung e wichtegen Indikator fir d'Flaachheet vum Wafer. Exzessiv Verzerrung beaflosst net nëmmen d'Placementgenauegkeet vum Wafer an der Veraarbechtungsausrüstung, mee kann och Problemer beim Chipverpackungsprozess verursaachen, wéi z. B. eng schlecht Bindung tëscht dem Chip an dem Verpackungsmaterial, wat dann d'Zouverlässegkeet vum Apparat beaflosst. An der High-End-Halbleiterproduktioun ginn d'Ufuerderunge fir Verzerrung ëmmer méi streng, fir den Ufuerderunge vun fortgeschrattene Chipproduktiouns- a Verpackungsprozesser gerecht ze ginn.

Kantenprofil: De Kantenprofil vun engem Wafer ass entscheedend fir seng spéider Veraarbechtung an Handhabung. E gëtt typescherweis duerch d'Kanteausschlusszon (EEZ) spezifizéiert, déi d'Distanz vum Waferrand definéiert, wou keng Veraarbechtung erlaabt ass. E richteg entworfene Kantenprofil an eng präzis EEZ-Kontroll hëllefen, Kantendefekter, Spannungskonzentratiounen an aner Problemer während der Veraarbechtung ze vermeiden, wouduerch d'Gesamtqualitéit an den Ausbezuelungsrendement vun de Wafer verbessert ginn. Bei verschiddene fortgeschrattene Produktiounsprozesser ass d'Prezisioun vum Kantenprofil op engem Submikronniveau erfuerderlech.

Partikelzuel: D'Zuel an d'Gréisstverdeelung vun de Partikelen op der Waferoberfläche beaflossen d'Leeschtung vu mikroelektroneschen Apparater wesentlech. Exzessiv oder grouss Partikelen kënnen zu Apparatausfäll féieren, wéi Kuerzschluss oder Leckage, wat d'Produktausbezuelung reduzéiert. Dofir gëtt d'Partikelzuel normalerweis gemooss andeems d'Partikelen pro Flächeneenheet gezielt ginn, wéi zum Beispill d'Zuel vu Partikelen, déi méi grouss wéi 0,3 μm sinn. Eng strikt Kontroll vun der Partikelzuel während der Waferherstellung ass eng essentiell Moossnam fir d'Produktqualitéit ze garantéieren. Fortgeschratt Botztechnologien an eng propper Produktiounsëmfeld ginn agesat fir d'Partikelkontaminatioun op der Waferoberfläche ze minimiséieren.

![]()

![]()

![]()

![]()

![]()

Verbonnen Produktioun

Eenkristall Siliziumwafer Si Substrat Typ N/P Optional Siliziumcarbidwafer

FZ CZ Si Wafer op Lager 12 Zoll Siliziumwafer Prime oder Test

Zäitpunkt vun der Verëffentlechung: 18. Abrëll 2025