SOI (Silizium-op-Isolator) Waferenrepresentéieren e spezialiséiert Hallefleitermaterial mat enger ultradënner Siliziumschicht, déi op enger isoléierender Oxidschicht geformt ass. Dës eenzegaarteg Sandwichstruktur bitt bedeitend Leeschtungsverbesserunge fir Hallefleiterkomponenten.

Strukturell Zesummesetzung:

Apparatschicht (iewescht Silizium):

D'Déckt reecht vu verschiddenen Nanometer bis Mikrometer, a déngt als aktiv Schicht fir d'Fabrikatioun vun Transistoren.

Vergräifte Oxidschicht (BOX):

Eng Siliziumdioxid-Isolatiounsschicht (0,05-15 μm Déck), déi d'Apparatschicht elektresch vum Substrat isoléiert.

Basissubstrat:

Bulksilizium (100-500 μm déck), dat mechanesch Ënnerstëtzung bitt.

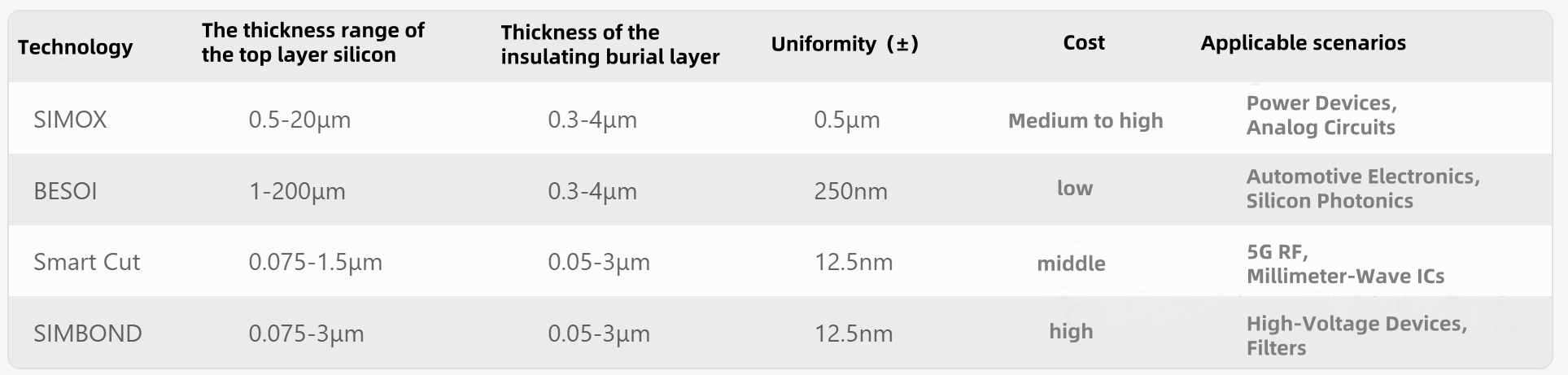

Jee no der Technologie vun der Virbereedungsprozess kënnen déi meescht üblech Prozesser vu SOI-Siliciumwaferen agedeelt ginn: SIMOX (Sauerstoffinjektiounsisolatiounstechnologie), BESOI (Bonding Thinning Technology) a Smart Cut (intelligent Stripping-Technologie).

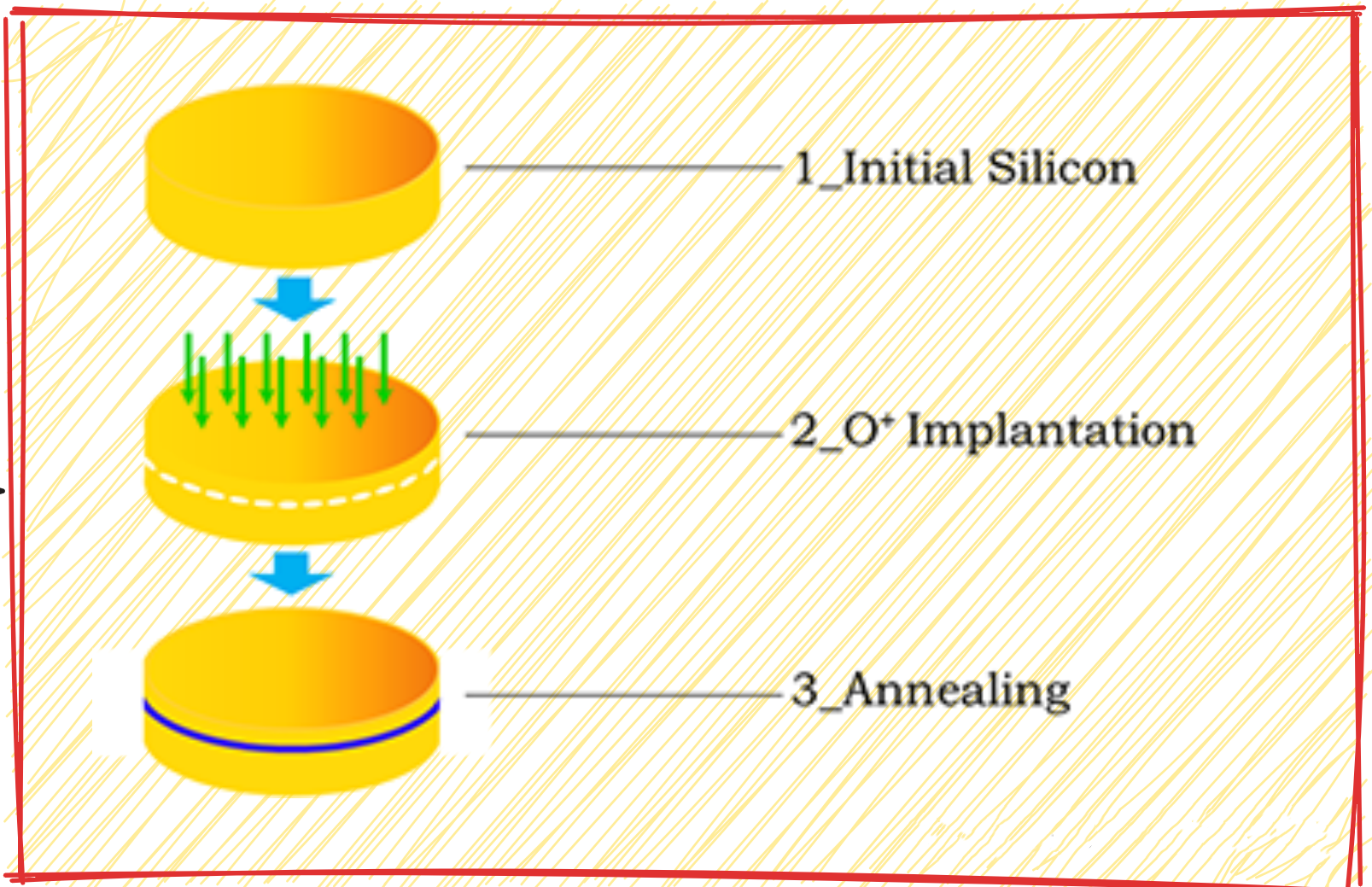

SIMOX (Oxygen injection isolation technology) ass eng Technik, bei där héichenergetesch Sauerstoffionen a Siliziumwafer injizéiert ginn, fir eng a Siliziumdioxid agebett Schicht ze bilden, déi dann enger Héichtemperaturglühung ënnerworf gëtt, fir Gitterdefekter ze reparéieren. De Kär ass direkt Ionen-Sauerstoffinjektioun, fir eng verstoppte Schicht Sauerstoff ze bilden.

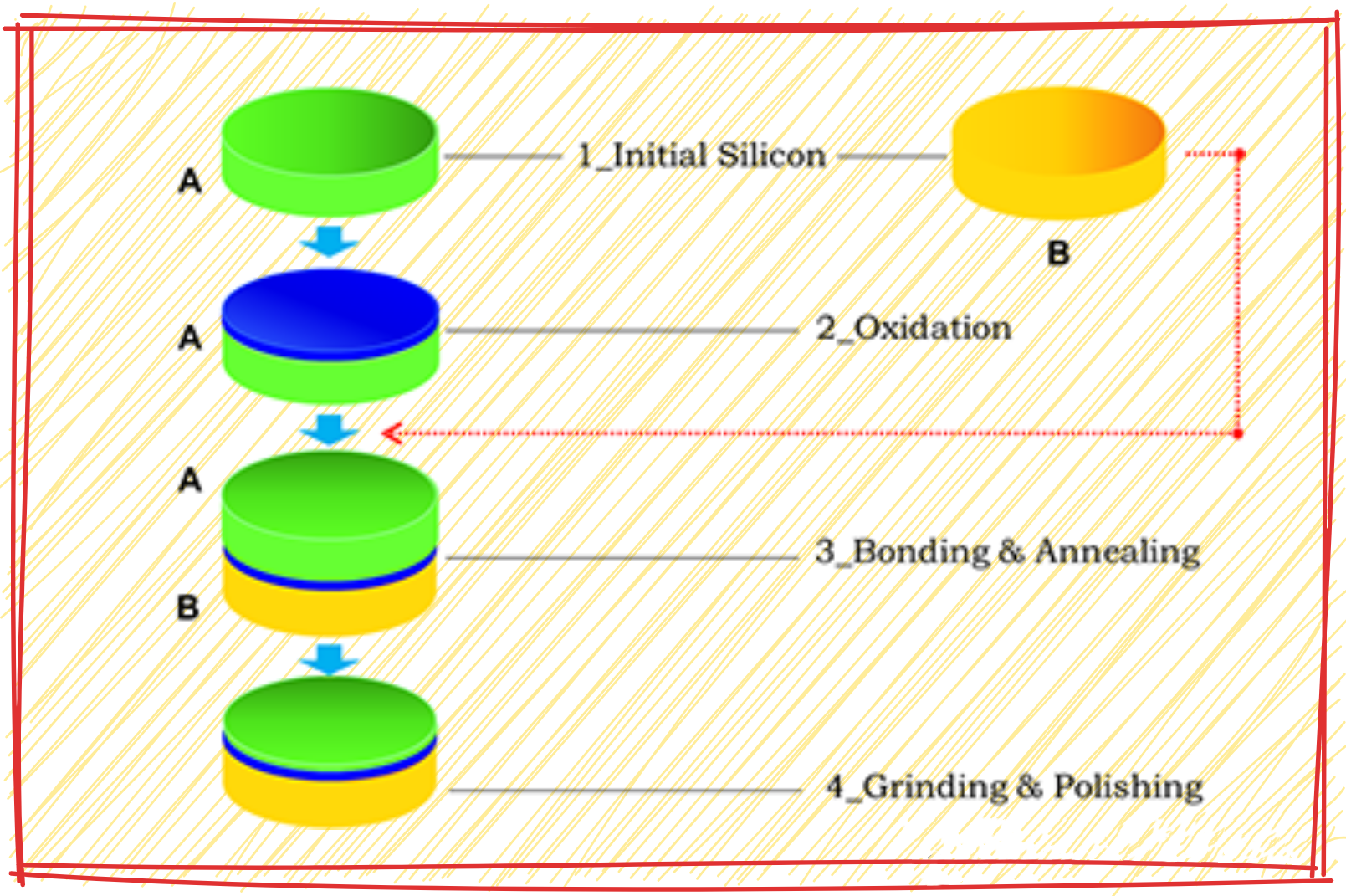

BESOI (Bonding Thinning Technology) besteet doran, zwou Siliziumwaferen ze verbannen an dann eng dovun duerch mechanescht Schleifen a chemescht Ätzen ze verdënnen, fir eng SOI-Struktur ze bilden. De Kär läit an der Bindung an der Verdënnung.

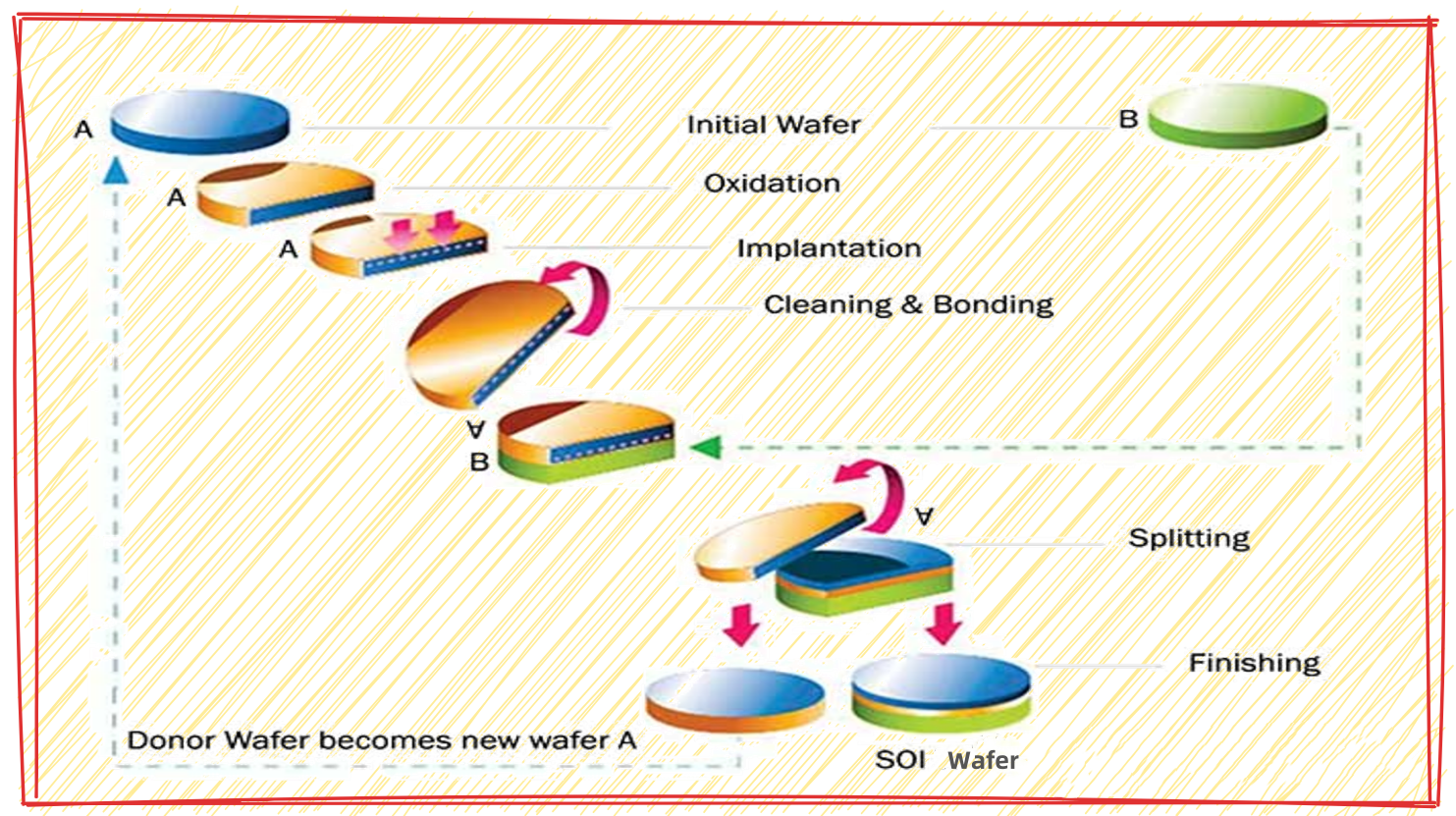

Smart Cut (Intelligent Exfoliation Technologie) bildt eng Peelingschicht duerch Waasserstoffioneninjektioun. Nom Binden gëtt eng Wärmebehandlung duerchgefouert, fir de Siliziumwafer laanscht d'Waasserstoffionenschicht ze peelen, wouduerch eng ultradënn Siliziumschicht entsteet. De Kär ass Waasserstoffinjektiounsstripping.

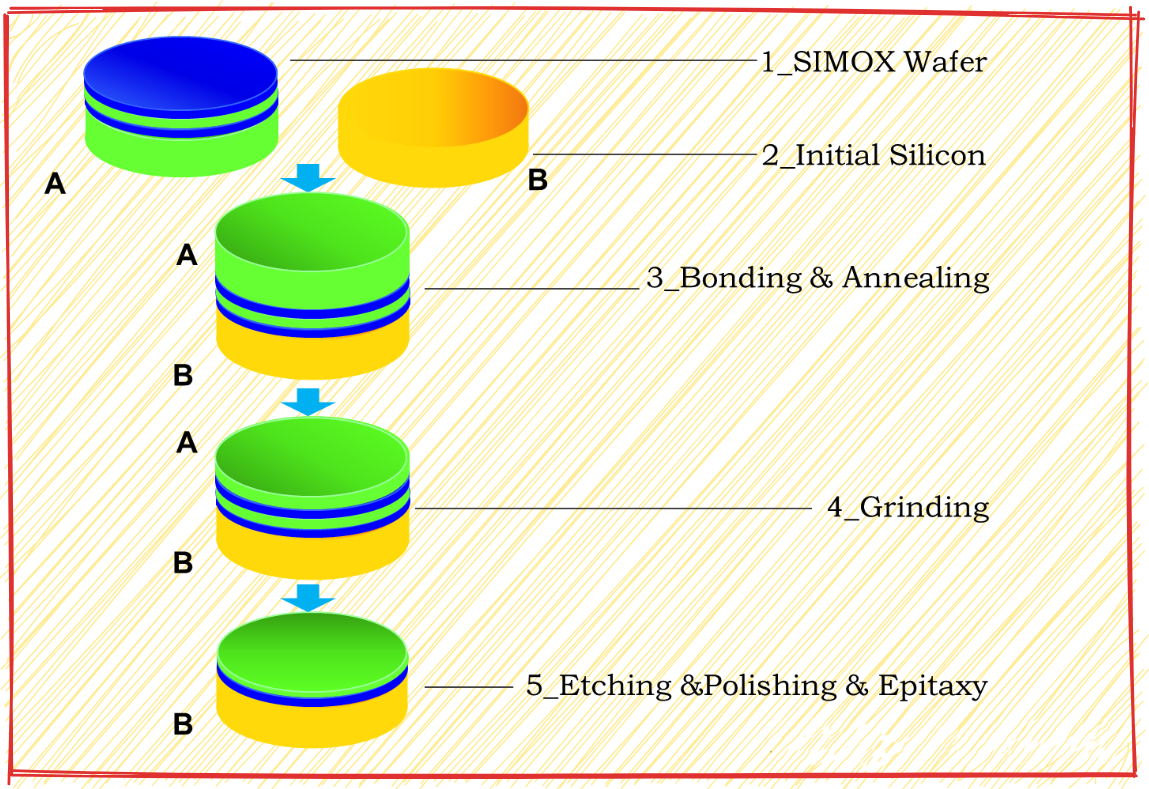

Aktuell gëtt et eng aner Technologie mam Numm SIMBOND (Oxygen Injection Bonding Technology), déi vu Xinao entwéckelt gouf. Tatsächlech ass et eng Method, déi Sauerstoffinjektiounsisolatioun an -bondingtechnologien kombinéiert. Bei dëser technescher Method gëtt den injizéierte Sauerstoff als eng dënnend Barrièreschicht benotzt, an déi tatsächlech verstoppte Sauerstoffschicht ass eng thermesch Oxidatiounsschicht. Dofir verbessert et gläichzäiteg Parameteren wéi d'Uniformitéit vum ieweschte Silizium an d'Qualitéit vun der verstoppter Sauerstoffschicht.

SOI-Siliciumwafer, déi no verschiddenen technesche Weeër hiergestallt ginn, hunn ënnerschiddlech Leeschtungsparameter a si fir verschidden Uwendungsszenarien gëeegent.

Déi folgend ass eng Zesummefassungstabell vun de Kärvirdeeler vun der Leeschtung vu SOI-Siliziumwaferen, kombinéiert mat hiren techneschen Eegeschaften an aktuellen Uwendungsszenarien. Am Verglach mat traditionellem Bulk-Silizium huet SOI bedeitend Virdeeler wat d'Gläichgewiicht tëscht Geschwindegkeet a Stroumverbrauch ugeet. (PS: D'Leeschtung vum 22nm FD-SOI ass no bei där vum FinFET, an d'Käschte gi ëm 30% reduzéiert.)

| Leeschtungsvirdeel | Technesche Prinzip | Spezifesch Manifestatioun | Typesch Uwendungsszenarien |

| Niddreg parasitär Kapazitéit | Isolatiounsschicht (BOX) blockéiert d'Ladekupplung tëscht dem Apparat an dem Substrat | D'Schaltgeschwindegkeet ass ëm 15%-30% eropgaang, de Stroumverbrauch ëm 20%-50% reduzéiert. | 5G RF, Héichfrequenzkommunikatiounschips |

| Reduzéierten Leckstroum | Isolatiounsschicht ënnerdréckt Leckstroumweeër | Leckstroum ëm >90% reduzéiert, Batterielaufzäit verlängert | IoT-Geräter, tragbar Elektronik |

| Verbessert Stralungshärkeet | Isoléierend Schicht blockéiert Stralungsinduzéiert Ladungsakkumulatioun | Stralungstoleranz 3-5x verbessert, reduzéiert Eenzelstéierungen | Raumschëffer, Ausrüstung fir d'Nuklearindustrie |

| Kuerzkanal-Effektkontroll | Dënn Siliziumschicht reduzéiert d'Interferenz vum elektresche Feld tëscht Drain a Source | Verbessert Schwellspannungsstabilitéit, optiméiert Ënnerschwellsteigung | Fortgeschratt Node-Logikchips (<14nm) |

| Verbessert thermesch Gestioun | Isolatiounsschicht reduzéiert d'Wärmeleitungskopplung | 30% manner Hëtztakkumulatioun, 15-25°C méi niddreg Betribstemperatur | 3D-ICs, Automotive Elektronik |

| Héichfrequenzoptimiséierung | Reduzéiert parasitär Kapazitéit a verbessert Trägermobilitéit | 20% méi niddreg Verzögerung, ënnerstëtzt >30GHz Signalveraarbechtung | mmWave Kommunikatioun, Satellittekommunikatiounschips |

| Erhéichte Designflexibilitéit | Kee Well-Doping erfuerderlech, ënnerstëtzt Réckverzerrung | 13%-20% manner Prozessschrëtt, 40% méi héich Integratiounsdicht | Mixed-Signal ICs, Sensoren |

| Immunitéit mat Latch-up | Isolatiounsschicht isoléiert parasitär PN-Verbindungen | De Schwellenwäert fir de Latch-up-Stroum ass op >100mA eropgaang | Héichspannungsapparater |

Zesummegefaasst sinn déi Haaptvirdeeler vum SOI: et leeft séier a verbraucht méi Energie.

Wéinst dësen Leistungseigenschaften vum SOI huet et breet Uwendungen a Beräicher, déi eng exzellent Frequenzleistung a Stroumverbrauchsleistung erfuerderen.

Wéi hei ënnendrënner gewisen, baséiert op dem Undeel vun den Uwendungsfelder, déi dem SOI entspriechen, kann een erkennen, datt HF- an Energieversuergungsapparater de groussen Deel vum SOI-Maart ausmaachen.

| Uwendungsfeld | Maartundeel |

| RF-SOI (Radiofrequenz) | 45% |

| Power SOI | 30% |

| FD-SOI (Vollstänneg ausgeschöpft) | 15% |

| Optesch SOI | 8% |

| Sensor-SOI | 2% |

Mam Wuesstem vu Mäert wéi mobil Kommunikatioun an autonomt Fueren, gëtt erwaart datt SOI-Siliciumwafers och eng gewësse Wuesstemsquote behalen.

XKH, als féierende Innovator an der Silicon-On-Insulator (SOI) Wafer Technologie, liwwert ëmfaassend SOI Léisungen vun der Fuerschung an Entwécklung bis zur Volumenproduktioun mat Hëllef vu brancheféierende Produktiounsprozesser. Eis komplett Portfolio enthält 200mm/300mm SOI Waferen, déi RF-SOI, Power-SOI an FD-SOI Varianten ëmfaassen, mat strenger Qualitéitskontroll, déi aussergewéinlech Leeschtungskonsistenz garantéiert (Dickeuniformitéit bannent ±1,5%). Mir bidden personaliséiert Léisungen mat enger Schichtdicke vun der Buried Oxid (BOX) vun 50nm bis 1,5μm a verschiddene Widderstandsspezifikatioune fir spezifesch Ufuerderungen ze erfëllen. Mat 15 Joer technescher Expertise an enger robuster globaler Versuergungskette liwwere mir zouverlässeg héichqualitativ SOI Substratmaterialien un Top-Hallefleederhersteller weltwäit, wat spitzen Chipinnovatiounen an der 5G Kommunikatioun, Automobilelektronik an Uwendungen vun kënschtlecher Intelligenz erméiglecht.

Zäitpunkt vun der Verëffentlechung: 24. Abrëll 2025