Resumé vun engem SiC-Wafer

Siliziumkarbid (SiC)-Waferensinn zum Substrat vun der Wiel fir Elektronik mat héijer Leeschtung, Héichfrequenz an Héichtemperatur am Automobil-, erneierbaren Energie- a Loftfaartsektor ginn. Eis Portfolio deckt Schlësselpolytypen an Dotierungsschemaen of - Stéckstoff-dotiert 4H (4H-N), héichreine Hallefisolatioun (HPSI), Stéckstoff-dotiert 3C (3C-N) a p-Typ 4H/6H (4H/6H-P) - a gëtt a dräi Qualitéitsgraden ugebueden: PRIME (voll poléiert Substrate fir Apparatqualitéit), DUMMY (iwwerlappt oder onpoléiert fir Prozesstester) a RESEARCH (personaliséiert Epi-Schichten an Dotierungsprofile fir Fuerschung an Entwécklung). Waferduerchmiesser erspanne vun 2″, 4″, 6″, 8″ an 12″, fir souwuel fir Legacy-Tools wéi och fir fortgeschratt Fabriken ze gëeegent. Mir liwweren och monokristallin Boules a präzis orientéiert Somkristaller fir den internen Kristallwuesstum z'ënnerstëtzen.

Eis 4H-N Wafere weisen Trägerdichten vun 1×10¹⁶ bis 1×10¹⁹ cm⁻³ a Widderstänn vun 0,01–10 Ω·cm, wat eng exzellent Elektronemobilitéit an Duerchbrochfelder iwwer 2 MV/cm liwwert - ideal fir Schottky-Dioden, MOSFETs a JFETs. HPSI-Substrater iwwerschreiden de Widderstand vun 1×10¹² Ω·cm mat Mikropipe-Dichten ënner 0,1 cm⁻², wat minimal Leckage fir RF- a Mikrowellengeräter garantéiert. Kubesch 3C-N, verfügbar a 2″- a 4″-Formater, erméiglecht Heteroepitaxie op Silizium a ënnerstëtzt nei photonesch an MEMS-Applikatiounen. P-Typ 4H/6H-P Wafere, mat Aluminium op 1×10¹⁶–5×10¹⁸ cm⁻³ dotiert, erliichteren komplementär Gerätearchitekturen.

SiC-Wafer, PRIME-Wafer ginn enger chemesch-mechanescher Poléierung bis zu enger RMS-Uewerflächenrauheet vun <0,2 nm, enger Gesamtdickenvariatioun vun ënner 3 µm an enger Béi vun <10 µm duerchgefouert. DUMMY-Substrater beschleunegen d'Montage- an d'Verpackungstester, während RESEARCH-Wafer Epi-Schicht-Déckte vun 2–30 µm an eng speziell Dotierung hunn. All Produkter sinn duerch Röntgendiffraktioun (Schaukelkurve <30 Bogensekonnen) a Raman-Spektroskopie zertifizéiert, mat elektreschen Tester – Hall-Miessungen, C-V-Profiling a Mikropipe-Scanning – déi d'Konformitéit mat JEDEC- a SEMI-Normen garantéieren.

Boules bis zu engem Duerchmiesser vun 150 mm ginn iwwer PVT a CVD mat Dislokatiounsdichten ënner 1×10³ cm⁻² a gerénger Mikropipezuel ugebaut. Somkristaller ginn bannent 0,1° vun der c-Achs geschnidden, fir e reproduzéierbart Wuesstum an héich Schneidrendementer ze garantéieren.

Duerch d'Kombinatioun vu verschiddene Polytypen, Dotierungsvarianten, Qualitéitsgraden, SiC-Wafergréissten, an interner Boule- a Seedkristallproduktioun, rationaliséiert eis SiC-Substratplattform d'Liwwerketten an beschleunegt d'Apparatentwécklung fir Elektroautoen, Smart Grids an Uwendungen an haarden Ëmweltbedingungen.

Resumé vun engem SiC-Wafer

Siliziumkarbid (SiC)-Waferensinn zum SiC-Substrat vun der Wiel fir Elektronik mat héijer Leeschtung, Héichfrequenz an Héichtemperaturen am Automobil-, erneierbaren Energie- a Loftfaartsektor ginn. Eis Portfolio deckt Schlësselpolytypen an Dotierungsschemaen of - Stéckstoff-dotiert 4H (4H-N), héichreine Hallefisolatioun (HPSI), Stéckstoff-dotiert 3C (3C-N) a p-Typ 4H/6H (4H/6H-P) - a gëtt an dräi Qualitéitsgraden ugebueden: SiC-WaferPRIME (voll poléiert Substrater a Gerätequalitéit), DUMMY (iwwerlappt oder ongepoléiert fir Prozesstester) a RESEARCH (personaliséiert Epi-Schichten an Dotierprofiler fir Fuerschung an Entwécklung). SiC-Waferduerchmiesser erreeche 2″, 4″, 6″, 8″ an 12″, fir souwuel fir al Tools wéi och fir fortgeschratt Fabriken ze gëeegent ze sinn. Mir liwweren och monokristallin Boules a präzis orientéiert Keimkristaller fir den internen Kristallwuesstum z'ënnerstëtzen.

Eis 4H-N SiC-Wafere weisen Trägerdichten vun 1×10¹⁶ bis 1×10¹⁹ cm⁻³ a Widderstänn vun 0,01–10 Ω·cm, wat eng exzellent Elektronemobilitéit an Duerchbrochfelder iwwer 2 MV/cm liwwert - ideal fir Schottky-Dioden, MOSFETs a JFETs. HPSI-Substrater iwwerschreiden de Widderstand vun 1×10¹² Ω·cm mat Mikropipe-Dichten ënner 0,1 cm⁻², wat minimal Leckage fir RF- a Mikrowellengeräter garantéiert. Kubesch 3C-N, verfügbar a 2″- a 4″-Formater, erméiglecht Heteroepitaxie op Silizium a ënnerstëtzt nei photonesch an MEMS-Applikatiounen. SiC-Wafer P-Typ 4H/6H-P-Wafere, déi mat Aluminium op 1×10¹⁶–5×10¹⁸ cm⁻³ dotiert sinn, erliichteren komplementär Gerätearchitekturen.

SiC-Wafer PRIME-Wafere ginn chemesch-mechanesch poléiert bis zu enger RMS-Uewerflächenrauheet vun <0,2 nm, enger Gesamtdickenvariatioun vun ënner 3 µm an enger Béi vun <10 µm. DUMMY-Substrater beschleunegen d'Montage- an d'Verpackungstester, während RESEARCH-Wafere Epi-Schicht-Déckte vun 2–30 µm an eng speziell Dotierung hunn. All Produkter sinn duerch Röntgendiffraktioun (Schaukelkurve <30 Bogensekonnen) a Raman-Spektroskopie zertifizéiert, mat elektreschen Tester – Hall-Miessungen, C-V-Profiling a Mikropipe-Scanning – déi d'Konformitéit mat JEDEC- a SEMI-Normen garantéieren.

Boules bis zu engem Duerchmiesser vun 150 mm ginn iwwer PVT a CVD mat Dislokatiounsdichten ënner 1×10³ cm⁻² a gerénger Mikropipezuel ugebaut. Somkristaller ginn bannent 0,1° vun der c-Achs geschnidden, fir e reproduzéierbart Wuesstum an héich Schneidrendementer ze garantéieren.

Duerch d'Kombinatioun vu verschiddene Polytypen, Dotierungsvarianten, Qualitéitsgraden, SiC-Wafergréissten, an interner Boule- a Seedkristallproduktioun, rationaliséiert eis SiC-Substratplattform d'Liwwerketten an beschleunegt d'Apparatentwécklung fir Elektroautoen, Smart Grids an Uwendungen an haarden Ëmweltbedingungen.

Datenblatt fir 6 Zoll 4H-N Typ SiC Wafer

| Datenblatt fir 6 Zoll SiC-Wafers | ||||

| Parameter | Ënnerparameter | Z-Klass | P-Klass | D-Klass |

| Duerchmiesser | 149,5–150,0 mm | 149,5–150,0 mm | 149,5–150,0 mm | |

| Déckt | 4H‑N | 350 µm ± 15 µm | 350 µm ± 25 µm | 350 µm ± 25 µm |

| Déckt | 4H‑SI | 500 µm ± 15 µm | 500 µm ± 25 µm | 500 µm ± 25 µm |

| Wafer Orientéierung | Off-Achs: 4,0° Richtung <11-20> ±0,5° (4H-N); Op der Achs: <0001> ±0,5° (4H-SI) | Off-Achs: 4,0° Richtung <11-20> ±0,5° (4H-N); Op der Achs: <0001> ±0,5° (4H-SI) | Off-Achs: 4,0° Richtung <11-20> ±0,5° (4H-N); Op der Achs: <0001> ±0,5° (4H-SI) | |

| Mikropäifdicht | 4H‑N | ≤ 0,2 cm⁻² | ≤ 2 cm⁻² | ≤ 15 cm⁻² |

| Mikropäifdicht | 4H‑SI | ≤ 1 cm⁻² | ≤ 5 cm⁻² | ≤ 15 cm⁻² |

| Widderstandsfäegkeet | 4H‑N | 0,015–0,024 Ω·cm | 0,015–0,028 Ω·cm | 0,015–0,028 Ω·cm |

| Widderstandsfäegkeet | 4H‑SI | ≥ 1×10¹⁰ Ω·cm | ≥ 1×10⁵ Ω·cm | |

| Primär flaach Orientéierung | [10-10] ± 5,0° | [10-10] ± 5,0° | [10-10] ± 5,0° | |

| Primär flaach Längt | 4H‑N | 47,5 mm ± 2,0 mm | ||

| Primär flaach Längt | 4H‑SI | Kerb | ||

| Randausgrenzung | 3 mm | |||

| Warp/LTV/TTV/Béi | ≤2,5 µm / ≤6 µm / ≤25 µm / ≤35 µm | ≤5 µm / ≤15 µm / ≤40 µm / ≤60 µm | ||

| Rauheet | Polnesch | Ra ≤ 1 nm | ||

| Rauheet | CMP | Ra ≤ 0,2 nm | Ra ≤ 0,5 nm | |

| Rëss um Rand | Keen | Kumulativ Längt ≤ 20 mm, eenzel ≤ 2 mm | ||

| Sechseckplacken | Kumulativ Fläch ≤ 0,05% | Kumulativ Fläch ≤ 0,1% | Kumulativ Fläch ≤ 1% | |

| Polytypgebidder | Keen | Kumulativ Fläch ≤ 3% | Kumulativ Fläch ≤ 3% | |

| Kuelestoffinklusiounen | Kumulativ Fläch ≤ 0,05% | Kumulativ Fläch ≤ 3% | ||

| Uewerflächenkratzer | Keen | Kumulativ Längt ≤ 1 × Waferduerchmiesser | ||

| Kantchips | Keen erlaabt ≥ 0,2 mm Breet & Déift | Bis zu 7 Chips, ≤ 1 mm all | ||

| TSD (Gewindespannverrécklung) | ≤ 500 cm⁻² | N/A | ||

| BPD (Basisplangverrécklung) | ≤ 1000 cm⁻² | N/A | ||

| Uewerflächenkontaminatioun | Keen | |||

| Verpackung | Multi-Wafer-Kassett oder Eenzel-Wafer-Behälter | Multi-Wafer-Kassett oder Eenzel-Wafer-Behälter | Multi-Wafer-Kassett oder Eenzel-Wafer-Behälter | |

Datenblatt fir 4 Zoll 4H-N Typ SiC Wafer

| Datenblatt fir 4 Zoll SiC Wafer | |||

| Parameter | Null MPD Produktioun | Standard Produktiounsgrad (P-Grad) | Dummy-Klass (Klass D) |

| Duerchmiesser | 99,5 mm–100,0 mm | ||

| Déckt (4H-N) | 350 µm ± 15 µm | 350 µm ± 25 µm | |

| Déckt (4H-Si) | 500 µm ± 15 µm | 500 µm ± 25 µm | |

| Wafer Orientéierung | Off-Achs: 4,0° Richtung <1120> ±0,5° fir 4H-N; Op der Achs: <0001> ±0,5° fir 4H-Si | ||

| Mikropäifdicht (4H-N) | ≤0,2 cm⁻² | ≤2 cm⁻² | ≤15 cm⁻² |

| Mikropäifdicht (4H-Si) | ≤1 cm⁻² | ≤5 cm⁻² | ≤15 cm⁻² |

| Widderstand (4H-N) | 0,015–0,024 Ω·cm | 0,015–0,028 Ω·cm | |

| Widderstand (4H-Si) | ≥1E10 Ω·cm | ≥1E5 Ω·cm | |

| Primär flaach Orientéierung | [10-10] ±5,0° | ||

| Primär flaach Längt | 32,5 mm ±2,0 mm | ||

| Sekundär flaach Längt | 18,0 mm ±2,0 mm | ||

| Sekundär flaach Orientéierung | Silikon-Uewerfläch no uewen: 90° mat der rietser Säit vun der Prime Flat ±5,0° | ||

| Randausgrenzung | 3 mm | ||

| LTV/TTV/Bogenverriegelung | ≤2,5 µm/≤5 µm/≤15 µm/≤30 µm | ≤10 µm/≤15 µm/≤25 µm/≤40 µm | |

| Rauheet | Polnesch Ra ≤1 nm; CMP Ra ≤0,2 nm | Ra ≤0,5 nm | |

| Kantrëss duerch héichintensivt Liicht | Keen | Keen | Kumulativ Längt ≤10 mm; eenzel Längt ≤2 mm |

| Sechseckplacken duerch héichintensivt Liicht | Kumulativ Fläch ≤0,05% | Kumulativ Fläch ≤0,05% | Kumulativ Fläch ≤0,1% |

| Polytypberäicher duerch héichintensivt Liicht | Keen | Kumulativ Fläch ≤3% | |

| Visuell Kuelestoffinklusiounen | Kumulativ Fläch ≤0,05% | Kumulativ Fläch ≤3% | |

| Siliziumoberfläche kraazt duerch héichintensivt Liicht | Keen | Kumulativ Längt ≤1 Waferduerchmiesser | |

| Kantchips duerch héichintensivt Liicht | Keen erlaabt ≥0,2 mm Breet an Déift | 5 erlaabt, ≤1 mm all | |

| Kontaminatioun vun der Siliziumoberfläche duerch héichintensivt Liicht | Keen | ||

| Verrécklung vun der Gewënnschraube | ≤500 cm⁻² | N/A | |

| Verpackung | Multi-Wafer-Kassett oder Eenzel-Wafer-Behälter | Multi-Wafer-Kassett oder Eenzel-Wafer-Behälter | Multi-Wafer-Kassett oder Eenzel-Wafer-Behälter |

Datenblatt fir 4 Zoll HPSI-Typ SiC-Wafer

| Datenblatt fir 4 Zoll HPSI-Typ SiC-Wafer | |||

| Parameter | Null MPD Produktiounsgrad (Z-Grad) | Standard Produktiounsgrad (P-Grad) | Dummy-Klass (Klass D) |

| Duerchmiesser | 99,5–100,0 mm | ||

| Déckt (4H-Si) | 500 µm ±20 µm | 500 µm ±25 µm | |

| Wafer Orientéierung | Off-Achs: 4,0° Richtung <11-20> ±0,5° fir 4H-N; Op der Achs: <0001> ±0,5° fir 4H-Si | ||

| Mikropäifdicht (4H-Si) | ≤1 cm⁻² | ≤5 cm⁻² | ≤15 cm⁻² |

| Widderstand (4H-Si) | ≥1E9 Ω·cm | ≥1E5 Ω·cm | |

| Primär flaach Orientéierung | (10-10) ±5,0° | ||

| Primär flaach Längt | 32,5 mm ±2,0 mm | ||

| Sekundär flaach Längt | 18,0 mm ±2,0 mm | ||

| Sekundär flaach Orientéierung | Silikon-Uewerfläch no uewen: 90° mat der rietser Säit vun der Prime Flat ±5,0° | ||

| Randausgrenzung | 3 mm | ||

| LTV/TTV/Bogenverriegelung | ≤3 µm/≤5 µm/≤15 µm/≤30 µm | ≤10 µm/≤15 µm/≤25 µm/≤40 µm | |

| Rauheet (C-Fläch) | Polnesch | Ra ≤1 nm | |

| Rauheet (Si-Fläch) | CMP | Ra ≤0,2 nm | Ra ≤0,5 nm |

| Kantrëss duerch héichintensivt Liicht | Keen | Kumulativ Längt ≤10 mm; eenzel Längt ≤2 mm | |

| Sechseckplacken duerch héichintensivt Liicht | Kumulativ Fläch ≤0,05% | Kumulativ Fläch ≤0,05% | Kumulativ Fläch ≤0,1% |

| Polytypberäicher duerch héichintensivt Liicht | Keen | Kumulativ Fläch ≤3% | |

| Visuell Kuelestoffinklusiounen | Kumulativ Fläch ≤0,05% | Kumulativ Fläch ≤3% | |

| Siliziumoberfläche kraazt duerch héichintensivt Liicht | Keen | Kumulativ Längt ≤1 Waferduerchmiesser | |

| Kantchips duerch héichintensivt Liicht | Keen erlaabt ≥0,2 mm Breet an Déift | 5 erlaabt, ≤1 mm all | |

| Kontaminatioun vun der Siliziumoberfläche duerch héichintensivt Liicht | Keen | Keen | |

| Verrécklung vun der Gewënnschraube | ≤500 cm⁻² | N/A | |

| Verpackung | Multi-Wafer-Kassett oder Eenzel-Wafer-Behälter | ||

Uwendung vun SiC-Waferen

-

SiC Wafer-Energiemodule fir EV-Inverter

SiC-Wafer-baséiert MOSFETs an Dioden, déi op héichwäertege SiC-Wafer-Substrater gebaut sinn, liwweren ultra-niddrege Schaltverloschter. Duerch d'Notzung vun der SiC-Wafer-Technologie funktionéieren dës Energieversuergungsmoduler bei méi héije Spannungen an Temperaturen, wat méi effizient Traktiounswandler erméiglecht. D'Integratioun vu SiC-Wafer-Chips an d'Energiestufen reduzéiert de Killbedarf an de Foussofdrock, wat dat vollt Potenzial vun der SiC-Wafer-Innovatioun weist. -

Héichfrequenz-RF- & 5G-Geräter op SiC-Wafer

HF-Verstärker a Schalter, déi op halbisoléierende SiC-Waferplattforme fabrizéiert sinn, weisen eng iwwerleeën Wärmeleitfäegkeet a Duerchbrochspannung op. De SiC-Wafer-Substrat miniméiert dielektresch Verloschter bei GHz-Frequenzen, während d'Materialstäerkt vum SiC-Wafer e stabile Betrib ënner héijen Leeschtungs- an Temperaturbedingungen erméiglecht, wat de SiC-Wafer zum Substrat vun der Wiel fir 5G-Basisstatiounen a Radarsystemer vun der nächster Generatioun mécht. -

Optoelektronesch & LED-Substrater aus SiC-Wafer

Blo an UV-LEDs, déi op SiC-Wafer-Substrater ugebaut ginn, profitéiere vun enger exzellenter Gitteranpassung an Hëtzofleedung. D'Benotzung vun engem poléierte C-Face SiC-Wafer garantéiert eenheetlech epitaktesch Schichten, während déi inherent Häert vum SiC-Wafer eng fein Waferverdënnung an eng zouverlässeg Verpackung vun den Apparater erméiglecht. Dëst mécht de SiC-Wafer zur bevorzugter Plattform fir héichleistungs- a laanglieweg LED-Applikatiounen.

Froen an Äntwerten iwwer SiC-Waferen

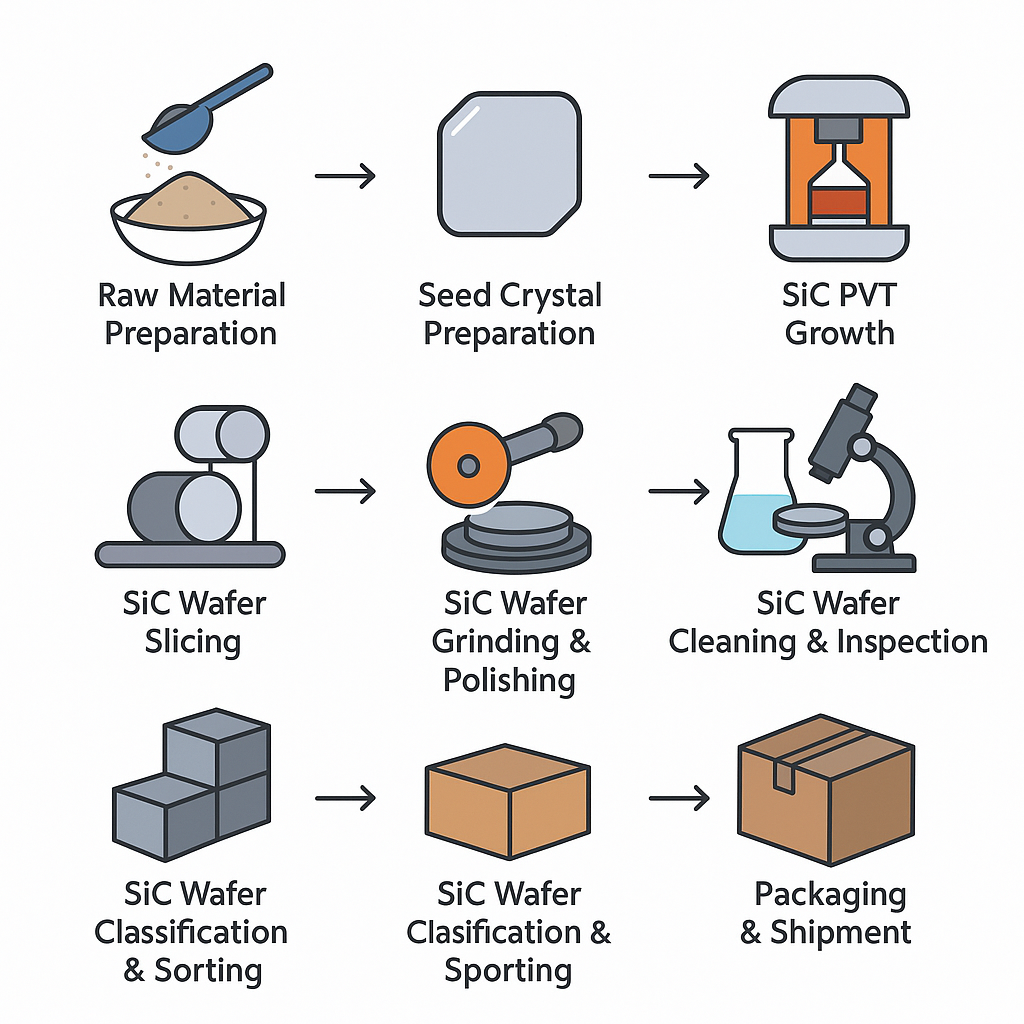

1. Q: Wéi gi SiC-Waferen hiergestallt?

A:

SiC-Waferen hiergestalltDetailéiert Schrëtt

-

SiC-WaferenVirbereedung vun der Réistoff

- Benotzt SiC-Pulver vun ≥5N (Onreinheeten ≤1 ppm).

- Sift a virbaken fir Reschter vu Kuelestoff- oder Stéckstoffverbindungen ze entfernen.

-

SiCVirbereedung vu Somkristaller

-

Huelt e Stéck 4H-SiC Eenzelkristall a schneid et laanscht d'Orientéierung 〈0001〉 op ~10 × 10 mm².

-

Präzisiounspoléieren op Ra ≤0,1 nm a Kristallorientéierung markéieren.

-

-

SiCPVT-Wuesstum (Physikaleschen Damptransport)

-

Graphit-Tigel lueden: ënnen mat SiC-Pulver, uewen mat Keimkristall.

-

Op 10⁻³–10⁻⁵ Torr evakuéieren oder mat héichreinem Helium bei 1 atm nofëllen.

-

D'Quellzon op 2100–2300 ℃ hëtzen, d'Saatzon op 100–150 ℃ méi kill halen.

-

Kontrolléiert d'Wuesstumsrate mat 1–5 mm/h fir Qualitéit an Duerchgank am Gläichgewiicht ze halen.

-

-

SiCGlühung vu Baren

-

De gewuessene SiC-Barr 4-8 Stonnen bei 1600–1800 ℃ glühen.

-

Zweck: thermesch Spannungen ofbauen an d'Verrécklungsdicht reduzéieren.

-

-

SiCWafer schneiden

-

Benotzt eng Diamant-Drotsäg fir de Barren a Wafere mat enger Déckt vun 0,5–1 mm ze schneiden.

-

Miniméiert Vibratiounen a lateral Kraaft fir Mikrorëss ze vermeiden.

-

-

SiCWaferSchleifen & Poléieren

-

Grob Schleifenfir Sägeschäden ze entfernen (Rauheet ~10–30 µm).

-

Fein Schleifenfir eng Flaachheet ≤5 µm z'erreechen.

-

Chemesch-mechanesch Poléieren (CMP)fir eng spigelähnlech Uewerfläch z'erreechen (Ra ≤0,2 nm).

-

-

SiCWaferBotzen & Inspektioun

-

Ultraschallreinigungan Piranha Léisung (H₂SO₄:H₂O₂), DI Waasser, dann IPA.

-

XRD/Raman Spektroskopiefir de Polytyp (4H, 6H, 3C) ze bestätegen.

-

Interferometriefir d'Flaachheet (<5 µm) an d'Verkrümmung (<20 µm) ze moossen.

-

Véierpunktsondefir de Widderstand ze testen (z.B. HPSI ≥10⁹ Ω·cm).

-

Defektinspektiounënner engem polariséierte Liichtmikroskop an engem Kratzestester.

-

-

SiCWaferKlassifikatioun & Sortéierung

-

Sortéiert d'Wafer no Polytyp an elektreschem Typ:

-

4H-SiC N-Typ (4H-N): Trägerkonzentratioun 10¹⁶–10¹⁸ cm⁻³

-

4H-SiC Héichreinheets-Hallefisolatioun (4H-HPSI): Widderstand ≥10⁹ Ω·cm

-

6H-SiC N-Typ (6H-N)

-

Anerer: 3C-SiC, P-Typ, etc.

-

-

-

SiCWaferVerpackung & Versand

2. Q: Wat sinn déi wichtegst Virdeeler vu SiC-Waferen am Verglach zu Siliziumwaferen?

A: Am Verglach mat Siliziumwaferen erméiglechen SiC-Waferen:

-

Betrib mat méi héijer Spannung(>1.200 V) mat engem méi niddrege Widderstand.

-

Méi héich Temperaturstabilitéit(>300 °C) a verbessert Wärmemanagement.

-

Méi séier Schaltgeschwindegkeetenmat méi niddrege Schaltverloschter, wat d'Ofkillung op Systemniveau an d'Gréisst vun de Stroumwandler reduzéiert.

4. Q: Wéi eng üblech Defekter beaflossen d'Ausbezuelung an d'Leeschtung vu SiC-Wafers?

A: Zu den Haaptdefekter a SiC-Waferen gehéieren Mikropipen, Basalplanverrécklungen (BPDs) a Kratzer op der Uewerfläch. Mikropipen kënne katastrophal Ausfäll vun den Apparater verursaachen; BPDs erhéijen den On-Resistenz mat der Zäit; a Kratzer op der Uewerfläch féieren zu Waferbroch oder engem schlechten epitaktischen Wuesstum. Eng grëndlech Inspektioun a Defektbekämpfung si dofir essentiell, fir de SiC-Wafer-Ausbezuelung ze maximéieren.

Zäitpunkt vun der Verëffentlechung: 30. Juni 2025