Aféierung an Siliziumkarbid

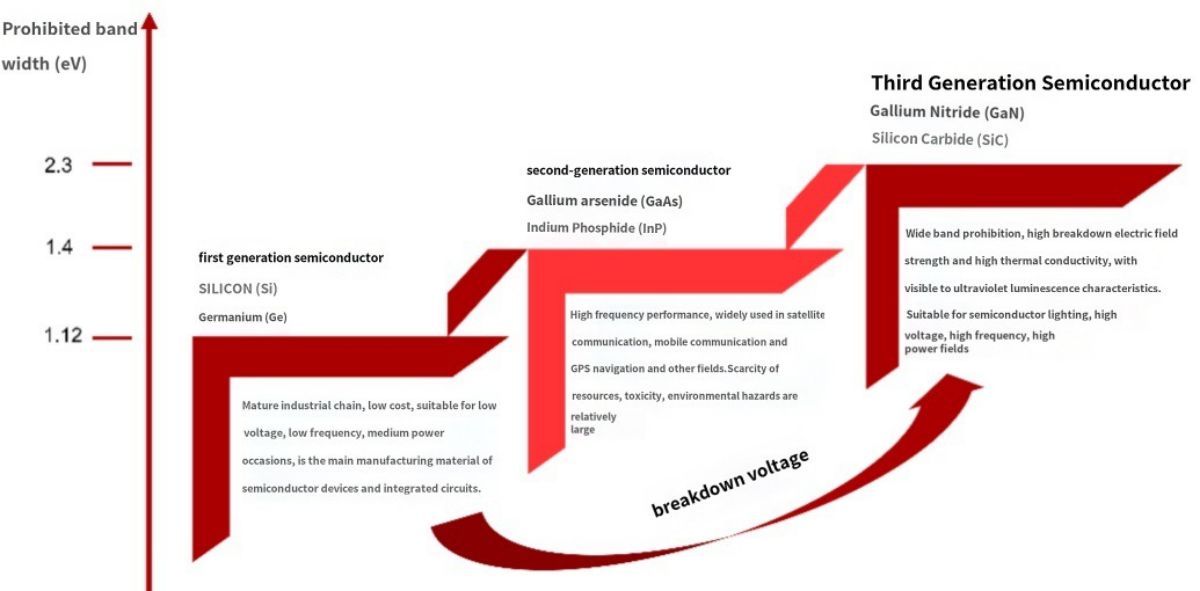

Siliziumkarbid (SiC) ass e verbonnent Hallefleedermaterial, dat aus Kuelestoff a Silizium besteet, an ee vun den ideale Materialien fir d'Fabrikatioun vun Héichtemperatur-, Héichfrequenz-, Héichleistungs- an Héichspannungsgeräter ass. Am Verglach mam traditionelle Siliziummaterial (Si) ass d'Bandlück vu Siliziumkarbid dräimol sou grouss wéi déi vu Silizium. D'Wärmeleitfäegkeet ass 4-5 Mol sou grouss wéi déi vu Silizium; d'Breakdownspannung ass 8-10 Mol sou grouss wéi déi vu Silizium; d'Elektronesch Sättigungsdriftquote ass 2-3 Mol sou grouss wéi déi vu Silizium, wat den Ufuerderunge vun der moderner Industrie fir Héichleistung, Héichspannung an Héichfrequenz entsprécht. Et gëtt haaptsächlech fir d'Produktioun vun Héichgeschwindegkeets-, Héichfrequenz-, Héichleistungs- an Liichtemittéierende elektronesche Komponenten benotzt. Zu den Downstream-Applikatiounsberäicher gehéieren Smart Grid, nei Energiefahrzeugen, photovoltaesch Wandenergie, 5G-Kommunikatioun, etc. Siliziumkarbiddioden a MOSFETs gi kommerziell agesat.

Héichtemperaturbeständegkeet. D'Bandlückebreet vu Siliziumkarbid ass 2-3 Mol sou grouss wéi déi vu Silizium, d'Elektronen wiesselen net einfach bei héijen Temperaturen a kënnen héije Betribstemperaturen aushalen, an d'Wärmeleitfäegkeet vu Siliziumkarbid ass 4-5 Mol sou grouss wéi déi vu Silizium, wat d'Wärmeofleedung vum Apparat méi einfach an d'Limitbetriebstemperatur méi héich mécht. Déi héich Temperaturbeständegkeet kann d'Leeschtungsdicht däitlech erhéijen an d'Ufuerderungen un de Killsystem reduzéieren, wouduerch den Terminal méi liicht a méi kleng gëtt.

Héichen Drock aushalen. D'Stäerkt vum elektresche Feld vum Duerchbroch vu Siliziumkarbid ass 10 Mol sou héich wéi déi vu Silizium, wat méi héije Spannungen aushale kann a besser fir Héichspannungsgeräter gëeegent ass.

Héichfrequenzwiderstand. Siliziumkarbid huet eng gesättigte Elektronendriftrate, déi duebel sou héich ass wéi Silizium, wat zu enger Ofwiesenheet vu Stroumverzögerung beim Ofschaltprozess féiert, wat d'Schaltfrequenz vum Apparat effektiv verbessere kann an d'Miniaturiséierung vum Apparat realiséiere kann.

Niddrege Energieverloscht. Am Verglach mat Siliziummaterial huet Siliziumcarbid e ganz niddregen Onwidderstand a niddregen Onverloscht. Gläichzäiteg reduzéiert déi héich Bandlückebreet vu Siliziumcarbid de Leckstroum an de Stroumverloscht däitlech. Zousätzlech huet de Siliziumcarbid-Apparat kee Stroumschleppphänomen beim Ofschaltprozess, an de Schaltverloscht ass niddreg.

Siliziumkarbidindustriekette

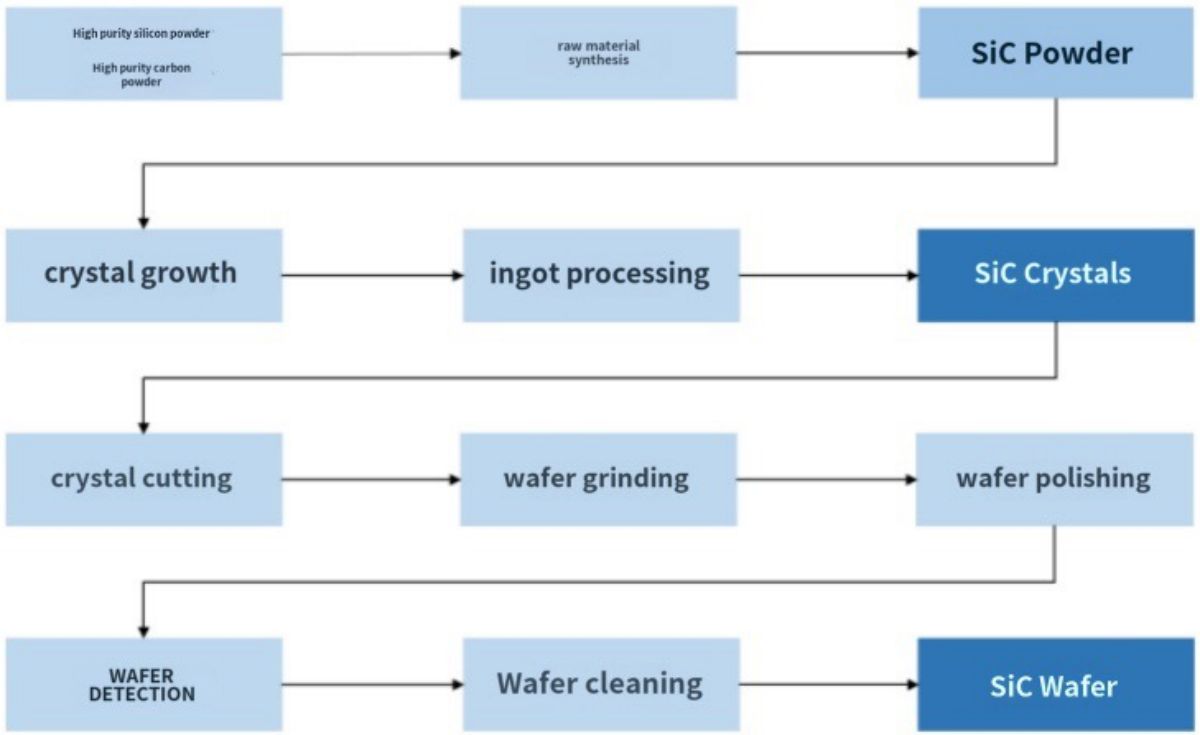

Et ëmfaasst haaptsächlech Substrat, Epitaxie, Apparatdesign, Fabrikatioun, Dichtung a sou weider. Siliziumkarbid vum Material bis zum Hallefleeder-Energiegerät wäert Eenzelkristallwuesstum, Barrenschneiden, Epitaxialwuesstum, Waferdesign, Fabrikatioun, Verpackung an aner Prozesser erliewen. Nom Synthese vum Siliziumkarbidpulver gëtt als éischt de Siliziumkarbidbarre gemaach, an dann gëtt de Siliziumkarbidsubstrat duerch Schneiden, Schleifen a Poléieren kritt, an d'epitaxial Plack gëtt duerch epitaxial Wuesstum kritt. Den epitaxialen Wafer gëtt aus Siliziumkarbid duerch Lithographie, Ätzen, Ionenimplantatioun, Metallpassivéierung an aner Prozesser hiergestallt, de Wafer gëtt an eng Form geschnidden, den Apparat gëtt verpackt, an den Apparat gëtt zu enger spezieller Schuel kombinéiert an zu engem Modul zesummegesat.

Upstream vun der Industriekette 1: Substrat - Kristallwuesstum ass de Kärprozess-Glied

Siliziumkarbid-Substrater maachen ongeféier 47% vun de Käschte vu Siliziumkarbid-Komponenten aus, déi héchst technesch Barrièren an der Produktioun an de gréisste Wäert, an representéieren de Kär vun der zukünfteger grousser Industrialiséierung vu SiC.

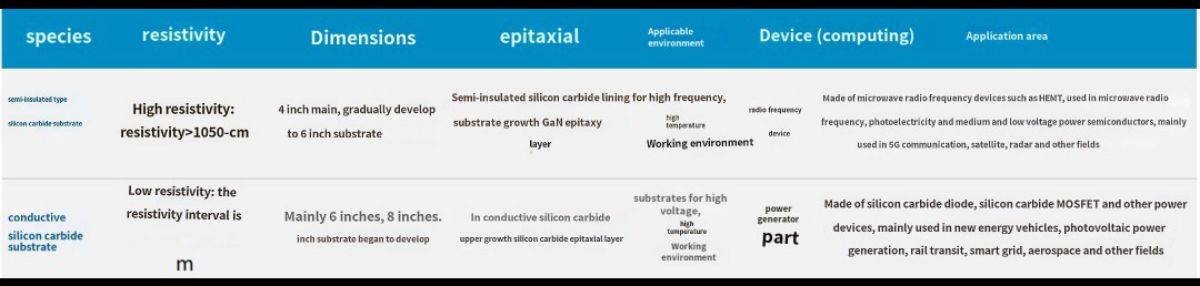

Aus der Perspektiv vun den Ënnerscheeder an den elektrochemeschen Eegeschafte kënnen Siliziumcarbid-Substratmaterialien a leetend Substrater (Widerstandsberäich 15~30mΩ·cm) a hallef-isoléiert Substrater (Widerstandsberäich méi héich wéi 105Ω·cm) opgedeelt ginn. Dës zwou Zorte vu Substrater gi benotzt fir diskret Apparater wéi Stroumversuergungsapparater a Radiofrequenzapparater no epitaktischem Wuesstum ze produzéieren. Dorënner gëtt hallef-isoléiert Siliziumcarbid-Substrat haaptsächlech bei der Fabrikatioun vu Galliumnitrid-HF-Apparater, photoelektreschen Apparater asw. benotzt. Duerch d'Wuesstum vun enger Gan-Epitaxialschicht op engem hallef-isoléierte SIC-Substrat gëtt d'Sic-Epitaxialplack virbereet, déi weider zu HEMT Gan-Isonitrid-HF-Apparater virbereet ka ginn. Leetend Siliziumcarbid-Substrat gëtt haaptsächlech bei der Fabrikatioun vu Stroumversuergungsapparater benotzt. Am Géigesaz zum traditionelle Produktiounsprozess vu Silizium-Energiegeräter kann de Siliziumcarbid-Energiegerät net direkt op dem Siliziumcarbid-Substrat hiergestallt ginn. D'Epitaxialschicht vu Siliziumcarbid muss op dem leitfäege Substrat ugewuess ginn, fir d'Epitaxialschicht vu Siliziumcarbid ze kréien, an d'Epitaxialschicht gëtt op Schottky-Dioden, MOSFETs, IGBTen an aner Energiegeräter hiergestallt.

Siliziumcarbidpulver gouf aus héichreinegem Kuelestoffpulver a Siliziumpulver mat héijer Reinheet synthetiséiert, an ënnerschiddlech Gréissten vu Siliziumcarbidbarren goufen ënner engem speziellen Temperaturfeld ugebaut, an duerno gouf e Siliziumcarbidsubstrat duerch verschidde Veraarbechtungsprozesser produzéiert. Den Haaptprozess ëmfaasst:

Rohmaterialsynthese: Den héichreine Siliziumpulver + Toner ginn no der Formel gemëscht, an d'Reaktioun gëtt an der Reaktiounskammer ënner héijer Temperatur iwwer 2000 °C duerchgefouert, fir d'Siliziumcarbidpartikelen mat spezifeschem Kristalltyp a Partikelgréisst ze synthetiséieren. Duerno ginn d'Prozesser duerch Zerbriechen, Sieben, Botzen an aner Prozesser duerchgefouert, fir d'Ufuerderunge vun den héichreine Siliziumcarbidpulver-Rohmaterialien ze erfëllen.

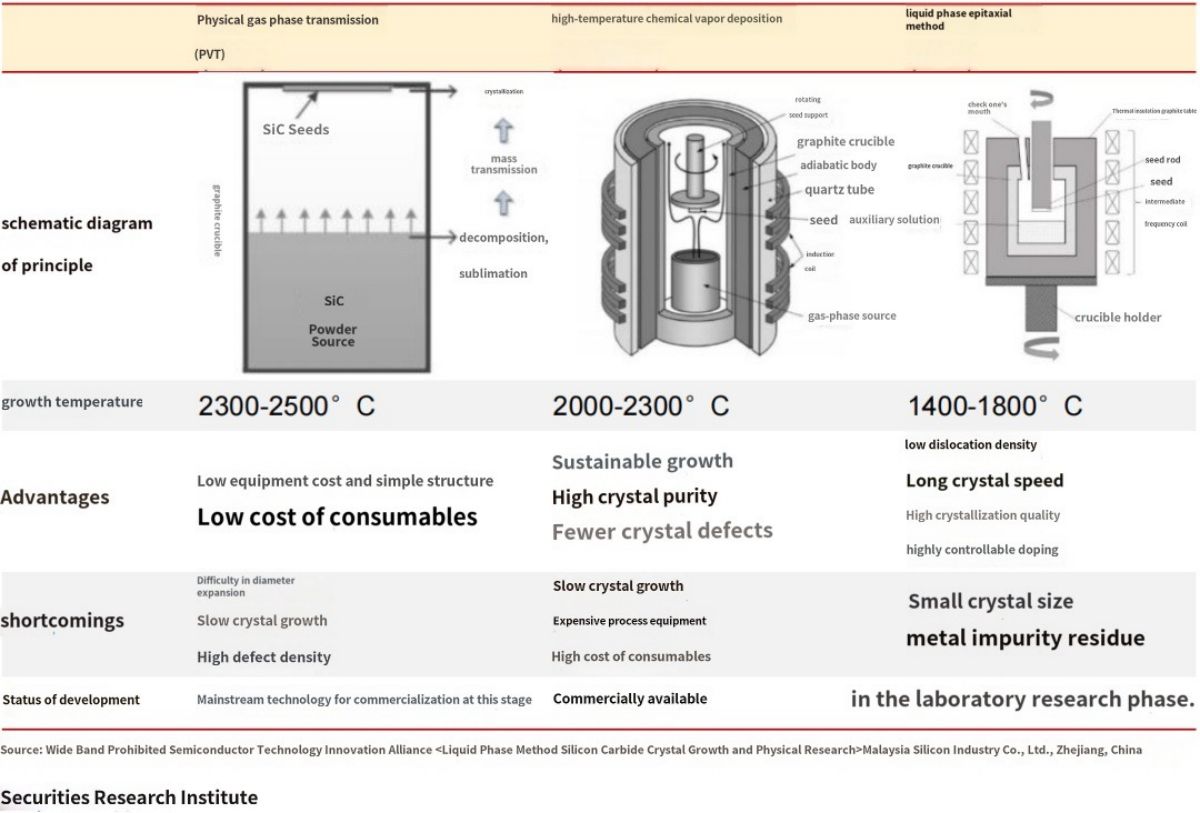

Kristallwuesstum ass de Kärprozess vun der Siliziumcarbid-Substratfabrikatioun, deen d'elektresch Eegeschafte vum Siliziumcarbid-Substrat bestëmmt. Am Moment sinn déi wichtegst Methode fir Kristallwuesstum physikalesch Dampftransfer (PVT), chemesch Dampfoflagerung bei héijer Temperatur (HT-CVD) a flësseg Phasen-Epitaxie (LPE). Dorënner ass d'PVT-Method déi aktuell Mainstream-Method fir de kommerzielle Wuesstum vu SiC-Substrater, mat der héchster technescher Reife an der am meeschte verbreeter an der Ingenieurswëssenschaft.

D'Virbereedung vum SiC-Substrat ass schwéier, wat zu sengem héije Präis féiert

D'Temperaturfeldkontroll ass schwéier: D'Wuesstum vun engem Si-Kristallstaaf brauch nëmmen 1500 ℃, während e SiC-Kristallstaaf bei enger héijer Temperatur iwwer 2000 ℃ muss gewuess ginn, an et gëtt méi wéi 250 SiC-Isomeren, awer déi wichtegst 4H-SiC-Eenkristallstruktur fir d'Produktioun vun Energieversuergungsgeräter kritt, wann se net präzis kontrolléiert gëtt, aner Kristallstrukturen. Zousätzlech bestëmmt den Temperaturgradient am Tiegel d'Geschwindegkeet vum SiC-Sublimatiounstransfer an d'Arrangement an de Wuesstumsmodus vun de gasfërmegen Atomer op der Kristallgrenzfläche, wat d'Kristallwuesstumsquote an d'Kristallqualitéit beaflosst, dofir ass et néideg, eng systematesch Temperaturfeldkontrolltechnologie ze schafen. Am Verglach mat Si-Materialien ass den Ënnerscheed an der SiC-Produktioun och an Héichtemperaturprozesser wéi Héichtemperatur-Ionenimplantatioun, Héichtemperatur-Oxidatioun, Héichtemperatur-Aktivéierung an dem Hardmaskprozess, deen duerch dës Héichtemperaturprozesser erfuerderlech ass.

Lues Kristallwuesstum: D'Wuesstumsquote vun engem Si-Kristallstaaf kann 30 ~ 150 mm/h erreechen, an d'Produktioun vun engem 1-3 m laange Siliziumkristallstaaf dauert nëmmen ongeféier 1 Dag; zum Beispill bei engem SiC-Kristallstaaf mat der PVT-Method ass d'Wuesstumsquote ongeféier 0,2-0,4 mm/h, et dauert 7 Deeg fir manner wéi 3-6 cm ze wuessen, d'Wuesstumsquote ass manner wéi 1% vum Siliziummaterial, an d'Produktiounskapazitéit ass extrem limitéiert.

Héich Produktparameter a niddreg Ausbezuelung: Zu de Kärparameter vum SiC-Substrat gehéieren d'Mikrotubuli-Dicht, d'Dislokatiounsdicht, de Widderstand, d'Verzerrung, d'Uewerflächenrauheet, etc. Et ass eng komplex Systemtechnik, Atomer an enger zouener Héichtemperaturkammer ze arrangéieren an de Kristallwuesstum ofzeschléissen, wärend gläichzäiteg d'Parameterindexe kontrolléiert ginn.

D'Material huet eng héich Häert, eng héich Bréchegkeet, eng laang Schnëttzäit a vill Verschleiss: D'Mohs-Häert vu SiC vun 9,25 ass nëmmen no Diamanten déi zweetgréisst, wat zu enger däitlecher Erhéijung vun der Schwieregkeet beim Schneiden, Schleifen a Poléieren féiert, an et dauert ongeféier 120 Stonnen fir 35-40 Stécker vun engem 3 cm décke Barren ze schneiden. Zousätzlech, wéinst der héijer Bréchegkeet vu SiC, ass de Verschleiss bei der Waferveraarbechtung méi grouss, an d'Ausgabverhältnis ass nëmmen ongeféier 60%.

Entwécklungstrend: Gréisstzounahme + Präisofgang

De weltwäite SiC-Maart fir 6-Zoll-Volumenproduktiounslinne reift, a féierend Firmen sinn op den 8-Zoll-Maart agaangen. Inlands Entwécklungsprojeten ëmfaassen haaptsächlech 6-Zoll. Am Moment, obwuel déi meescht inlands Firmen nach ëmmer op 4-Zoll-Produktiounslinne baséieren, expandéiert d'Industrie lues a lues op 6-Zoll. Mat der Reife vun der 6-Zoll-Ënnerstëtzungsausrüstungstechnologie verbessert sech och déi inlands SiC-Substrattechnologie lues a lues. D'Skalenvirdeeler vu grousse Produktiounslinne wäerten sech reflektéieren, an den aktuellen Zäitënnerscheed vun der inlandser 6-Zoll-Masseproduktioun huet sech op 7 Joer verklengert. Déi méi grouss Wafergréisst kann zu enger Erhéijung vun der Zuel vun eenzelne Chips féieren, d'Ausbezuelungsquote verbesseren an den Undeel vun de Kantenchips reduzéieren, an d'Käschte fir Fuerschung an Entwécklung an den Ausbezuelungsverloscht ginn op ongeféier 7% gehale, wouduerch d'Waferauslastung verbessert gëtt.

Et gëtt nach ëmmer vill Schwieregkeeten beim Design vun Apparater

D'Kommerzialiséierung vu SiC-Dioden gëtt lues a lues verbessert. De Moment hunn eng Rei vun inlännesche Produzenten SiC SBD-Produkter entwéckelt. Mëttel- a Héichspannungs-SiC SBD-Produkter hunn eng gutt Stabilitéit. Am Gefier-OBC gëtt SiC SBD+SI IGBT benotzt fir eng stabil Stroumdicht z'erreechen. De Moment gëtt et keng Barrièren am Patentdesign vu SiC SBD-Produkter a China, an den Ënnerscheed mat Ausland ass kleng.

SiC MOS huet nach ëmmer vill Schwieregkeeten, et gëtt nach ëmmer eng Lück tëscht SiC MOS an auslännesche Produzenten, an déi relevant Produktiounsplattform ass nach ëmmer am Opbau. Am Moment hunn ST, Infineon, Rohm an aner 600-1700V SiC MOS d'Masseproduktioun erreecht a mat ville Fabrikatiounsindustrien ënnerschriwwen a geliwwert, während den aktuellen inlännesche SiC MOS Design bal fäerdeg ass, eng Rei vun Designhersteller mat Fabriken an der Wafer-Flow-Phase schaffen, an eng spéider Clientverifizéierung brauch nach eng Zäit, sou datt et nach eng laang Zäit bis zur groussskaleger Kommerzialiséierung ass.

Aktuell ass déi planar Struktur déi allgemeng Wiel, an den Trench-Typ gëtt an Zukunft wäit verbreet am Héichdrockberäich benotzt. Et gëtt vill Hiersteller vu SiC MOS Planarstrukturen. D'Planarstruktur verursaacht am Verglach mat der Groove keng lokal Panneproblemer, wat d'Stabilitéit vun der Aarbecht beaflosst. Um Maart ënner 1200V ass d'Applikatiounswäert breet. D'Planarstruktur ass relativ einfach am Fabrikatiounsberäich, fir d'Herstellungsfäegkeet an d'Käschtekontroll op zwou Aspekter ze erfëllen. D'Groven-Apparat huet d'Virdeeler vun extrem gerénger parasitärer Induktivitéit, schneller Schaltgeschwindegkeet, niddrege Verloschter a relativ héijer Leeschtung.

2--SiC Wafer Neiegkeeten

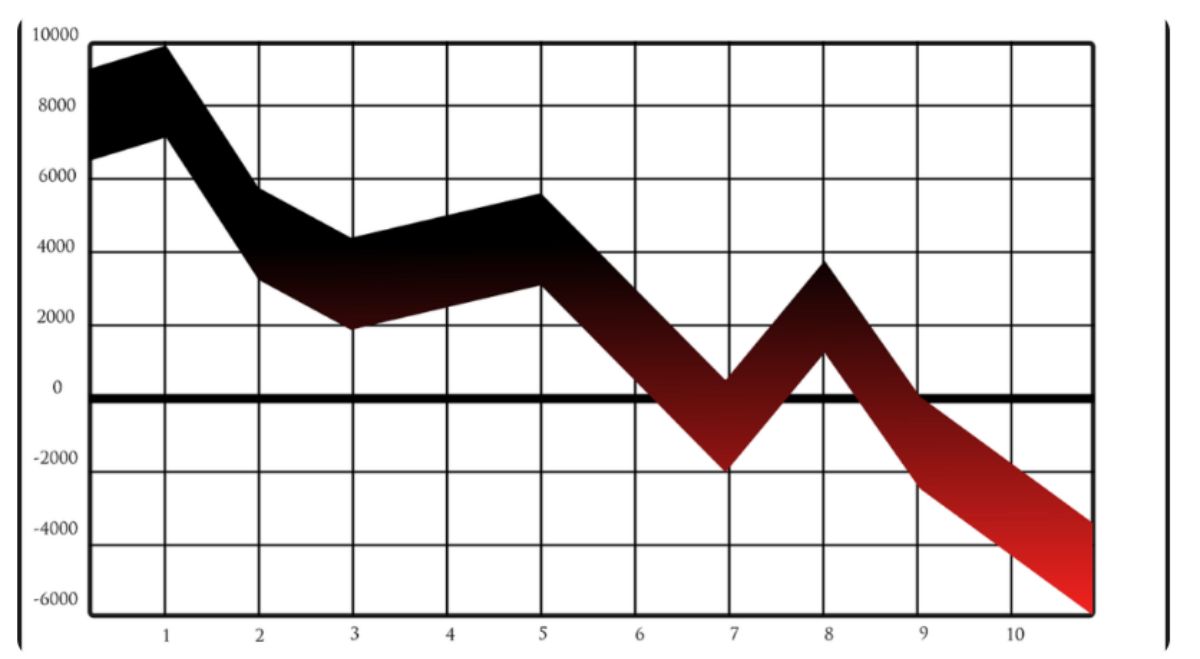

Produktioun a Verkafswuesstem um Siliziumkarbidmaart, Opmierksamkeet op dat strukturellt Ongläichgewiicht tëscht Offer an Nofro

Mat dem schnelle Wuesstem vun der Maartnofro fir Héichfrequenz- a Leeschtungselektronik ass de physikalesche Limit vun Halbleiterbauelementer op Siliziumbasis lues a lues prominent ginn, an d'Halbleitermaterialien vun der drëtter Generatioun, déi duerch Siliziumkarbid (SiC) vertrueden sinn, sinn lues a lues industrialiséiert ginn. Wat d'Materialleistung ugeet, huet Siliziumkarbid eng dräimol sou grouss Bandlückebreet wéi e Siliziummaterial, eng zéngmol sou grouss Stäerkt vum elektresche Feld beim kriteschen Duerchbroch an eng dräimol sou héich Wärmeleitfäegkeet, sou datt Siliziumkarbid-Energiebauelementer fir Héichfrequenz-, Héichdrock-, Héichtemperatur- an aner Uwendungen gëeegent sinn an hëllefen, d'Effizienz an d'Leeschtungsdicht vun elektronesche Leeschtungssystemer ze verbesseren.

Aktuell sinn SiC-Dioden a SiC-MOSFETs lues a lues op de Maart komm, an et gëtt méi reif Produkter, dorënner ginn SiC-Dioden a verschiddene Beräicher wäit verbreet amplaz vu Silizium-baséierten Dioden benotzt, well se net de Virdeel vun der Réckwärtsrecuperatioun hunn; SiC-MOSFETs ginn och lues a lues an der Automobilindustrie, Energiespeicherung, Ladestäb, Photovoltaik an anere Beräicher agesat; Am Beräich vun den Automobilanwendungen gëtt den Trend vun der Modulariséierung ëmmer méi prominent, an déi iwwerleeën Leeschtung vu SiC muss op fortgeschratt Verpackungsprozesser vertrauen, fir dat z'erreechen. Technesch gesinn, mat enger relativ reifer Schueldichtung als Mainstream, ass d'Zukunft vun der Plastikdichtungsentwécklung méi gëeegent fir SiC-Moduler. Seng personaliséiert Entwécklungscharakteristike si méi gëeegent fir SiC-Moduler.

Siliziumkarbid Präisreduktiounsgeschwindegkeet oder iwwer d'Fantasie eraus

D'Uwendung vu Siliziumkarbid-Bauelementer ass haaptsächlech duerch déi héich Käschte limitéiert. De Präis vun engem SiC MOSFET ass ënner dem selwechten Niveau 4 Mol méi héich wéi dee vun engem Si-baséierten IGBT. Dëst läit dorun, datt de Prozess vu Siliziumkarbid komplex ass, wou d'Wuesstum vun Eenzelkristaller an Epitaktika net nëmmen ëmweltfrëndlech ass, mä och d'Wuesstumsquote lues ass, an d'Veraarbechtung vun Eenzelkristaller an de Substrat muss duerch e Schnëtt- a Polierprozess goen. Baséierend op den eegene Materialcharakteristiken an der onreifer Veraarbechtungstechnologie ass den Ausbezuele vum haushaltssubstrat manner wéi 50%, a verschidde Faktoren féieren zu héije Substrat- an Epitaktikapräisser.

Wéi och ëmmer, d'Käschtezesummesetzung vu Siliziumkarbid-Bauelementer an Silizium-baséierten Bauelementer ass diametral géigeniwwer, d'Substrat- an d'Epitaxialkäschte vum Frontkanal maachen 47% respektiv 23% vum gesamten Bauelement aus, insgesamt ongeféier 70%, den Design, d'Fabrikatioun an d'Dichtungsverbindunge vum Bauelement vum Réckkanal maachen nëmmen 30% aus, d'Produktiounskäschte vu Silizium-baséierten Bauelementer konzentréiere sech haaptsächlech op d'Waferfabrikatioun vum Réckkanal mat ongeféier 50%, an d'Substratkäschte maachen nëmmen 7% aus. D'Phenomeen vum Wäert vun der Siliziumkarbidindustriekette op d'Kopp gestallt bedeit, datt Upstream-Substratepitaxie-Hiersteller e Kärrecht hunn, wat de Schlëssel zum Layout vun inlänneschen an auslännesche Betriber ass.

Aus dynamescher Siicht um Maart bedeit d'Reduktioun vun de Käschte vu Siliziumcarbid, zousätzlech zur Verbesserung vum Siliziumcarbid-Langkristall an dem Schneidprozess, d'Erweiderung vun der Wafergréisst, wat och e reife Wee an der Hallefleederentwécklung an der Vergaangenheet war. Wolfspeed-Donnéeë weisen datt d'Verbesserung vum Siliziumcarbid-Substrat vu 6 Zoll op 8 Zoll d'Produktioun vu qualifizéierte Chips ëm 80%-90% erhéije kann an doduerch d'Ausbezuelung verbessert. Dëst kann déi kombinéiert Eenheetskäschte ëm 50% reduzéieren.

2023 ass bekannt als dat "éischt Joer vun 8-Zoll SiC". Dëst Joer beschleunegen d'Hiersteller vu Siliziumkarbid aus dem Inland an aus dem Ausland de Layout vun 8-Zoll Siliziumkarbid. Zum Beispill huet Wolfspeed eng Investitioun vun 14,55 Milliarden US-Dollar fir d'Expansioun vun der Siliziumkarbidproduktioun gemaach, e wichtegen Deel dovun ass de Bau vun enger 8-Zoll SiC-Substratfabrik. Fir déi zukünfteg Versuergung mat 200 mm SiC-Blankmetall un eng Rei vu Firmen ze garantéieren, hunn déi national Tianyue Advanced an Tianke Heda och laangfristeg Ofkommes mat Infineon ënnerschriwwen, fir an Zukunft 8-Zoll Siliziumkarbid-Substrater ze liwweren.

Vun dësem Joer un wäert Siliziumkarbid vu 6 Zoll op 8 Zoll wuessen. Wolfspeed erwaart, datt bis 2024 d'Eenheetschipkäschte vun engem 8-Zoll-Substrat am Verglach zu de Eenheetschipkäschte vun engem 6-Zoll-Substrat am Joer 2022 ëm méi wéi 60% reduzéiert ginn, an datt de Präisréckgang de Applikatiounsmaart weider opmaache wäert, sou d'Fuerschungsdaten vu Ji Bond Consulting. Den aktuellen Maartundeel vun 8-Zoll-Produkter ass manner wéi 2%, an et gëtt erwaart, datt de Maartundeel bis 2026 op ongeféier 15% wiisst.

Tatsächlech kann de Réckgang vum Präis vum Siliziumcarbid-Substrat d'Virstellunge vu ville Leit iwwerschreiden. Déi aktuell Maartoffer fir 6-Zoll-Substrater läit bei 4000-5000 Yuan/Stéck. Am Verglach zum Ufank vum Joer ass de Präis staark gefall a gëtt erwaart, datt en nächst Joer ënner 4000 Yuan fale wäert. Et ass derwäert ze bemierken, datt verschidde Produzenten, fir den éischte Maart ze gewannen, de Verkafspräis op eng méi niddreg Käschtelinn reduzéiert hunn. Dëst huet de Präiskrich opgemaach, deen haaptsächlech op d'Offer vu Siliziumcarbid-Substrater am Nidderspannungsberäich konzentréiert ass. D'Offer vum Siliziumcarbid-Substrat am Nidderspannungsberäich ass relativ ausreechend. D'Inland- an auslännesch Produzenten erweideren hir Produktiounskapazitéit aggressiv oder loossen d'Iwwerangebot vum Siliziumcarbid-Substrat méi fréi ufänken wéi erwaart.

Zäitpunkt vun der Verëffentlechung: 19. Januar 2024